# ED29116

DESIGNING

WITH THE Am29116

16-BIT

BIPOLAR MICROPROCESSOR

LECTURE VOLUME II

#### ED29116

"Designing with the Am29116 16-Bit Bipolar Microprocessor"

bу

Barbara Albert Arndt Bode, Dr. rer. nat. J.W. Locke, Ph.D.

March 1983

Customer Education Center Advanced Micro Devices, Inc.

Copyright by

ADVANCED MICRO DEVICES, INC.

9Ø1 Thompson Place

Sunnyvale

California 94Ø86

1983

#### INDEX to VOLUME II

| Day 2                                                                                                                                                                                                                                                                                                                            | page                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 3. Exercises on the Am29116, part 1 Exercises Solutions                                                                                                                                                                                                                                                                          | 3.1Ø<br>3.2Ø<br>3.8Ø                                                                       |

| 4. Am29116 Bit-Mapped Graphics Controllers Introduction Drawing a Vector Fast Vector-Plotting Algorithm Am29116 Microcode for Vector Generation - Improving the Vector Algorithm                                                                                                                                                 | 4.1Ø<br>4.2Ø<br>4.3Ø<br>4.5Ø<br>4.8Ø<br>4.11Ø                                              |

| 5. Application of the Am29116 for intelligent controllers Intelligent controller structures low speed version high speed version comparison with an Am2901 based solution very high speed solution - Am9520 burst error processor - Microprogramming the controller                                                              | 5.1¢<br>5.15<br>5.3¢<br>5.11¢<br>5.17¢<br>5.22¢<br>5.24¢<br>5.425                          |

| 6. Application of the Am29116 for general purpose CPUs  A Microprogrammed CPU using Am29116  System overview  System Organization  Instruction Formats  Timing analysis  Pipelining at the Macro level  Comparison with Super-16  o Macro Instruction Execution  Comparison for 2901-29203-29116 solutions  Performance Analysis | 6.10<br>6.20<br>6.30<br>6.40<br>6.60<br>6.130<br>6.190<br>6.270<br>6.340<br>6.430<br>6.450 |

| 7. Exercises on the Am29116, part 2 Exercises (Microprogramming the Am29116) Solutions                                                                                                                                                                                                                                           | 7.1Ø<br>7.2Ø<br>7.3Ø                                                                       |

DAY 2

CHAPTER 3

Exercises, Part 1

#### Exercises - Part 1

#### True or false:

- 1. The Am29116 is externally TTL compatible, but uses ECL circuitry internally.

- 2. The Am29116 is expandable (i.e. two can be hooked together).

- 3. The Am29116 is for 8-bit or 16-bit intelligent controllers.

- 4. The Am29116 can perform conditional testing on its status register.

- 5. The barrel shifter rotates 1 to 15 bits up or down in one microcycle.

- 6. The Am29116 must be used with an Am2904.

- 7. The Am29116 can perform immediate operations.

- 8. The Am29116 has a choice of four input sources to its data MUX's which in turn provide three ALU inputs, R, S, U.

- 9. The Am29116 can perform three-address instructions.

- $1\emptyset$ . Fast clock speed is synonymous with high throughput.

- 11. The Am29116 can generate remainders up to 16 bits long from CRC polynomials.

- 12. The Am29116 always has its ALU output at  $Y_i$ .

- 13. The ALU destinations are RAM, ACC, D-Latch.

- 14. Single-operand instructions are PASS, COMPLEMENT, INCREMENT, and TWO's COMPLEMENT.

- 15.  $D(\emptyset E)$  (D with zero extend) is used for two's-complement arithmetic.

- 16. "R --> Dest" calculates one's-complement, and "R + 1 --> Dest" calculates two's complement.

- 17. The Am29116 can perform NAND, NOR, EXOR in one microcycle.

- 18. Shift up can use  $\emptyset$ , 1 or the QLINK bit as input to the LSB.

- 19. Shift down uses  $\emptyset$ , 1 or the QLINK bit as the only input choices to the MSB.

- 20. Rotate operates in byte or word mode.

- 21. Rotate uses the U-input to the ALU.

- 22. Load  $2^n$  causes a mask (1 in a field of  $\emptyset$ 's) to be generated and can be used for loading RAM, ACC.

- 23. Read Y-bus, change a bit, output to Y-bus is possible in one microcycle with the Am29116.

- 24. If you perform a bit-oriented instruction on the ACC, the destination is the ACC or the RAM.

- 25. There are 17 possible results when priority encoding a word.

- 26. Byte-mode prioritizing ignores bits 8-15.

- 27. The Am29116 can perform operations on polynomials of degree 16 or less.

- 28. 95% of CRC calculations use polynomials with 16-bit remainders.

- 29. The CRC calculations can be done in a forward or reverse mode. (i.e. either transmit bit  $\emptyset$  first or transmit bit 15 first)

- 3Ø. CRC remainders can be calculated in byte or word mode.

- 31. The status word can be loaded from D, RAM, or ACC.

- 32. The Z, C, N and OVR status bits can be loaded without affecting LINK or the user flags.

- 33. You can set or reset the entire status word.

- 34. You can set or reset the ALU flags individually.

- 35. On the Am29116, you can load both the status register and the ACC in the same microcycle if the RAM is the source.

- 36. If the status-register enable is high, the status register is "frozen". That is, no operation can alter status.

- 37. All conditional testing is performed on the stored values in the status register.

Fill in or answer:

- 38. How many bits are in the Am29116 status register?

- 39. How many conditional tests can be made?

- $4\emptyset$ . Can you perform a conditional test during another instruction? If so, how?

- 41. Can byte operations be performed in either the upper byte or the lower byte of a register?

- 42. Can the Am29116 support a 100 ns microcycle time?

- 43. List three possible sources for single operand instructions.

- 44. Can you load a byte into the D-latch?

- 45. List three possible source pairs for two-operand instructions.

- 46. Show the content of this register after a word-mode rotate with n=2.

- 47. Does the Am29116 allow you to rotate R3 and place the result back into R3?

- 48. Does the Am29116 allow you to rotate R3 and place the result in R7?

- 49. If there is no active priority request, what result is produced by a prioritize instruction in word mode?

- $5\emptyset$ . If bit 15 is active, what result is produced by a prioritize instruction in word mode?

- 51. If bit 15 is active, what result is produced by a prioritize instruction in byte mode?

- 52. Is it true that the Am29116 is an order of magnitude faster than the Am2901 which in turn is an order of magnitude faster than the AmZ8000 for certain controller-oriented operations?

- 53. Can the Am29116 be used to do multiply? If so, outline the required code.

- 54. Can the Am29116 be used for bit operations?

- 55. Can the Am29116 be used for rotate operations?

- 56. Does the Am29116 have an ALU?

- 57. Can the Am29116 be used to build a CPU?

- 58. If a mask bit is zero in a ROTATE-and-MERGE instruction, from which operand is the corresponding bit passed to the destination?

- 59. If  $U = \emptyset \emptyset 11$   $\emptyset \emptyset \emptyset 1$   $\emptyset 1 \emptyset 1$   $\emptyset 1 1 \emptyset$   $R = 1 \emptyset 1 \emptyset$   $1 \emptyset 0 \emptyset$   $1 \emptyset 0 \emptyset$   $1 \emptyset 0 \emptyset$   $1 \emptyset 0 \emptyset$

what bit pattern is produced by a word-mode ROTATE-and-MERGE instruction with n=4?

- $6\emptyset.$  If the highest bit position with a one is position 7 and the mask is  $1\emptyset 1\emptyset$   $_{\mbox{HEX}},$  what is the result of a <code>word-mode</code> prioritize instruction?

- 61. If the highest bit position with a one is position 7 and the mask is 1010 HEX, what is the result of a byte-mode prioritize instruction?

- 62. What is the result of loading the complement of  $2^n$ ? What type of instruction allows you to do this?

- 63. Suppose you want to do a word-rotate down five bit positions. How do you do this on an Am29116?

- 64. What is QLINK?

- 65. Can you set and reset the ALU status bits individually as you can with the Am29 $\phi$ 4 micro-status register?

- 66. Can you set & reset the LINK and FLAG status bits individually?

- 67. In byte mode, are all 8 bits of the status register loaded?

- 68. Which instructions do <u>not</u> cause the ALU status bits to be updated?

- 69. When are the upper four status bits (LINK, FLAG1, FLAG2, FLAG3) changed?

Exercises - Part 1

SOLUTIONS

- 1. True

- 2. False

- 3. True almost every instruction operates in byte or word mode.

- 4. True using either the instruction lines  $\rm I_1$   $\rm I_4$  or the  $\rm T_1$   $\rm T_4$  lines.

- 5. False the barrel shifter only rotates <u>up</u> 1 to 15 bits. An effective down rotate is achieved by choosing an appropriate number of bits to rotate up such that the result is equivalent to the desired down rotation. (16-i in word mode; 8-i in byte mode)

- 6. False but an Am29Ø4 is useful for emulations because of its bit-settable status register.

- 7. True requires two microwords and two microcycles.

- 8. True ACC, D-Latch, RAM and the instruction lines (for immediate data).

- 9. False the Am29116 can be extended only to a two-register-address structure (using an external MUX, an additional 5-bit microinstruction field and extended timing).

- 10. False! recall the problems that occur on branching with a double-pipelined CPU based on Am2910 & Am2901 or Am2903 and the need for extra NOP instructions.

- 11. True

- 12. True  $\underline{if}$   $\overline{OE}_y$  is enabled. Otherwise, false.

- 13. True with reservations the D-latch can be used but requires some tricky timing. You could generate a race condition if the D-latch is also a source for the operation. The D-latch is <u>not intended</u> to be a destination, and its use as such is <u>not recommended</u>.

"Normal" destinations are RAM, ACC or NONE.

- 14. True. (PASS is another term for MOVE).

- 15. False D(SE) (D sign-extended from bit 7)

is used for two's complement arithmetic

- 16. True

- 17. True

- 18. True shift uses the  $\emptyset$ , 1 or QLINK. The inputs to the carry MUX should not be confused with the inputs to the shift MUX.

- 19. False QC, QN $\theta$ QOVR and QLINK are also available. Do not confuse the use of Q in the Am29116 context (designating status-register contents) with the Q-shifter or Q-register of Am29 $\phi$ 1, Am29 $\phi$ 3 and Am292 $\phi$ 3.

- 20. True

- 21. True

- 22. True also goes to internal Y-bus

- 23. True be careful with the timing

- 24. False ACC only.

BONR instruction has common source/destination field.

- 25. True none and 1 thru 16.

- 26. True

- 27. True

- 28. True according to an AMD survey.

- 29. True

- 3Ø. False Word mode only. But short polynomials that produce an 8-bit remainder can be used.

- 31. True the status can also be loaded from immediate data as well.

- 32. True

- 33. True

- 34. False if you need this use an Am29Ø4.

- 35. False this is the one source which precludes loading both the ACC and the status register.

- 36. True

- 37. True

Answers to Fill-in or Answer Section:

- 38. Eight Z, C, N, OVR, LINK, FLAG1, FLAG2, FLAG3

- 39. There are 12 condition code test signals You can test all 8 status bits individually. You can force a LOW. And you can test 3 combinations:  $Z+\overline{C}$ , N $\theta$ OVR, (N $\theta$ OVR)+Z.

- 4Φ. Yes by using the T-bus lines as input. This requires a wider microword to control the T-bus.

- 41. In byte mode, instructions alter only the lower byte.

- 42. Yes <u>Very carefully!</u>

This requires a register between the sequencer and the control store as well as the pipeline register at the output of the control store. 125 ns is more easily achieved.

- 43. RAM, ACC, D, I, Zero.

- 44. No.

- 45. RAM ACC, RAM I, D RAM, D ACC, ACC I, D I

- 46. Rotate is up only -

1100 1010 0011 0101 n = 2 becomes 0010 1000 1101 0111

- 47. Yes

- 48. Yes with an external MUX and care with timing.

- 49. Zero.

- 5Ø. One.

- 51. Bit 15 does not participate in the byte mode.

The result will depend on the content of the lower byte.

- 52. Yes it is true. Especially when multi-bit rotation, priority determination or CRC remainder calculations are needed.

53. Yes - but it was not optimized for this application.

Consider a  $16 \times 16$ -bit unsigned multiplication:

- i) Initialize the partial product (PP) and a counter to zero.

- ii) Increment the counter.

- iii) Test the MSB of the multiplier If the MSB is a one then: PP+multiplicand --> PP

- iv) If count equals 16 then END else upshift the PP and the multiplier. (remember to carry from the LSH to the MSH of the PP)

- v) Goto ii).

Look at the Am29116 instruction set! We can write a better procedure for the Am29116 than the above.

With the use of the prioritize and the rotate instructions you can reduce the number of microcycles. (But now the number of microcycles depends on the multiplier!)

An improved algorithm is as follows:

- i) Initialize PP and counter to zero.

- ii) Prioritize the multiplier & call the result 'prio'. If (prio  $\approx \emptyset$ ) OR (prio > (16-counter)) then rotate PP by (16-counter) and END.

- iii) count+prio --> count

- iv) Rotate PP and multiplier by prio.

- v) PP+multiplicand --> PP

- vi) Goto ii).

- 54. Yes

- 55. Yes The barrel shifter works in the byte or word mode.

- 56. Yes The Am29116 has a 16-bit three-operand ALU.

- 57. Yes but it was not optimized for this application.

- 58. The R-operand bit is passed to the destination.

- 59. The result is 1011 000 1110 0011.

- 60. The result is 9. Note: <mask bit i equal to zero> allows participation of the source bit i in the priority determination.

- 61. The result is one.

- 62. This clears the n<sup>th</sup> bit and sets all of the other bits in the destination. The instruction is: 'BOR1, LDC2NR' or 'BONR, LDC2NA' or 'BONR, LDC2NY'.

- 63. Rotate up with n=11. ... (16-5=11)

- 64. QLINK is the linkage bit for shift operations. It is also used by CRC instructions to bring in each bit of serial data.

- 65. You cannot set/reset the ALU status bits one by one. If you need this feature, use the Am2904 as an additional external status logic.

- 66. Yes

- 67. In byte mode, the lower  $\underline{4}$  bits (ALU status) on the status register are loaded.

- 68. NOOP, save-status, test-status or any instruction if either of  $\overline{\text{IEN}}$  or  $\overline{\text{SRE}}$  are high.

- 69. The upper four status bits (LINK, FLAG 1, FLAG 2, FLAG 3) are changed during status set/reset; status load (word mode only); plus QLINK is updated after each shift

#### CHAPTER 4

Am29116 Bit-Mapped Graphics Controllers

#### Am29116 Bit-Mapped Graphics Controllers

The Am29116 has proved to be very popular amongst designers of graphics controllers. This is a natural result of the fact that the Am29116 has a very suitable instruction set for the kinds of algorithms that arise in graphics applications.

We will first discuss this subject in general using the article\* by Chu and Miller as a reference. Then we will examine in detail one of the most useful procedures for bit-mapped raster scan graphics, the efficient drawing of a straight vector, and show how this is coded for the Am29116. By taking both an overall look at the requirements of bit-mapped graphics and by following a particular algorithm in detail, we are going to demonstrate why the Am29116 has been so successful as a graphics controller.

\* "Microprocessor Architecture Suits Bit-Mapped Graphics"

by Paul Chu and Warren Miller, Electronic Design, Jan.20,1983 p.143

#### Am29116 Bit-Mapped Graphics Controllers (continued)

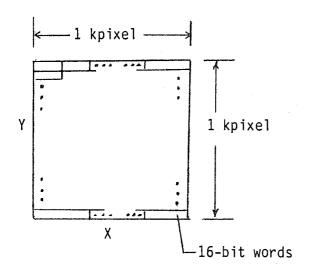

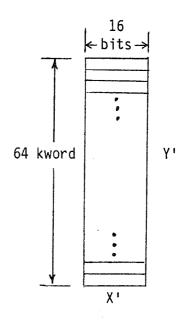

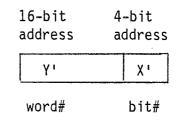

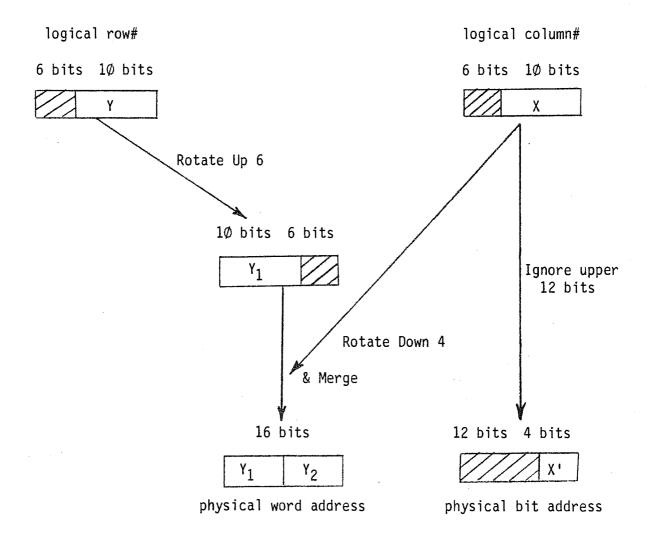

#### Logical Address to Physical Address Mapping

Display Memory (logical)

10-bit 10-bit address

Y

X

row#

column#

Bit-Map Memory (physical)

4-26

Am29116 Bit-Mapped Graphics Controllers (continued)

Logical Address to Physical Address Mapping (continued)

#### The mapping process:

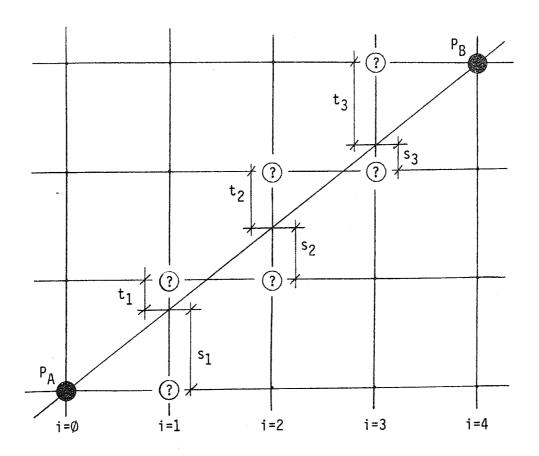

### Drawing a Vector on a Two-Dimensional Raster Grid

We would like to find an efficient procedure to draw a straight vector between two points. When given the coordinates of two end points,  $P_A$  and  $P_B$ , located on a raster grid, the procedure should set the bits in screen memory associated with these end points and with a set of intermediate points closely approximating a straight line. We will describe a procedure that works for lines of unit or less slope that selects the closer of the two candidate points for each increment of 'x'. That is, for each 'i' in the above figure, the procedure will compare the lengths of 's $_{\rm i}$ ' and 't $_{\rm i}$ ' and will select the point associated with the shorter length. This procedure can be generalized to handle lines with slope exceeding unity.

#### Drawing a Vector on a Two-Dimensional Raster Grid (continued)

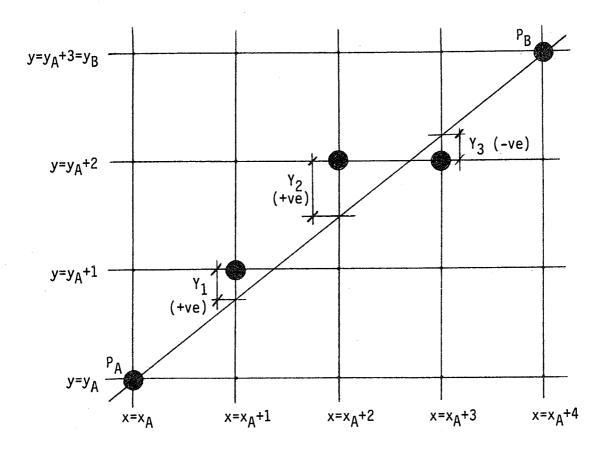

- of course at  $x=x_A$  and  $x=x_B$ ,  $Y=\emptyset$

In the above figure we see a successful application of such a procedure. Since the intermediate points are selected from a finite grid, they do not lie precisely on the ideal straight line linking  $P_A$  with  $P_B$ . A measure of the success of the procedure is the value of the  $Y_i$ 's, the differences between the y-coordinates of the intermediate points and the corresponding vertical position of the ideal line.

#### An Algorithm for Fast Vector Plotting with an Am29116

For a straight line linking two points  $P_A(x_A, y_A)$  and  $P_B(x_B, x_B)$ :

$$y = y(x) = \frac{(y_B - y_A)x + x_By_A - x_Ay_B}{x_B - x_A}$$

Let us define  $dy=(y_B-y_A)$  and  $dx=(x_B-x_A)$ . For an arbitrary point  $P(x_p,y_p)$ , not necessarily on this line:

$$Y_p = (y_p - y(x_p)) \cdot dx = -x_p \cdot dy + y_p \cdot dx - x_B y_A + x_A y_B$$

is proportional to the vertical distance of P from the line. We multiplied the distance by 'dx' to obtain a measure of vertical distance that can be calculated without performing a division. In all further discussion we will use this scaled measure for vertical distances. Since we will apply the same scale factor, 'dx', to all vertical distances, this tactic will not affect our ability to determine which of two points is closer to an ideal line.

A simple vector-drawing procedure is as follows:

- 1. Plot a point at  $x_A, y_A$ .

- 2. Increment x by one.

- 3. If  $x > x_B$  then quit.

- 4. Calculate Y, the vertical distance error, scaled by 'dx', for two points: x,y and x,y+1.

- 5. If ABS(Y(x,y)) < ABS(Y(x,y+1)) then goto 6 else y=y+1.

- 6. Plot a point at x,y.

- 7. Goto 2.

This procedure may be referred to as a <u>digital differential analyser</u> by analogy with numerical methods for solving differental equations. This procedure has avoided division and multiplication but it still has redundant arithmetic. Two additions are required for the two Y's, we may have to perform a two's-complement operation on either or both of the Y's to produce absolute values and finally a subtraction is required to compare the Y's. We can compress this procedure further.

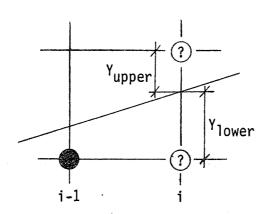

We have been choosing the next point based on the sign of

$$d = ABS(Y_{lower}) - ABS(Y_{upper})$$

(We will now call 'd' the "discriminant" for our problem).

#### An Algorithm for Fast Vector Plotting with an Am29116 (continued)

But in the situation shown below,  $Y_{lower}$  is negative and  $Y_{upper}$  is positive. In this case:

$$d = -Y_{1ower} - Y_{upper}$$

and the absolute-value operation is not required.

Further the  $i^{th}$  discriminant can be obtained efficiently from the (i-1)<sup>th</sup> discriminant. To discover how, consider the Y's involved:

$$Y_{i-1} = -x_{i-1} \cdot dy + y_{i-1} \cdot dx - x_B y_A + x_A y_B$$

$Y_{lower_i} = -(x_{i-1} + 1) \cdot dy + y_{i-1} \cdot dx - x_B y_A + x_A y_B = Y_{i-1} - dy$

$Y_{upper_i} = -(x_{i-1} + 1) \cdot dy + (y_{i-1} + 1) \cdot dx - x_B y_A + x_A y_B = Y_{i-1} - dy + dx$

Therefore:

$$d_i = -Y_{lower} - Y_{upper} = -2Y_{i-1} + 2 \cdot dy - dx$$

And since  $Y_{\emptyset} = \emptyset$ :  $d_1 = 2 \cdot dy - dx$

$$d_1 = 2 \cdot dy - dx$$

#### An Algorithm for Fast Vector Plotting with an Am29116 (continued)

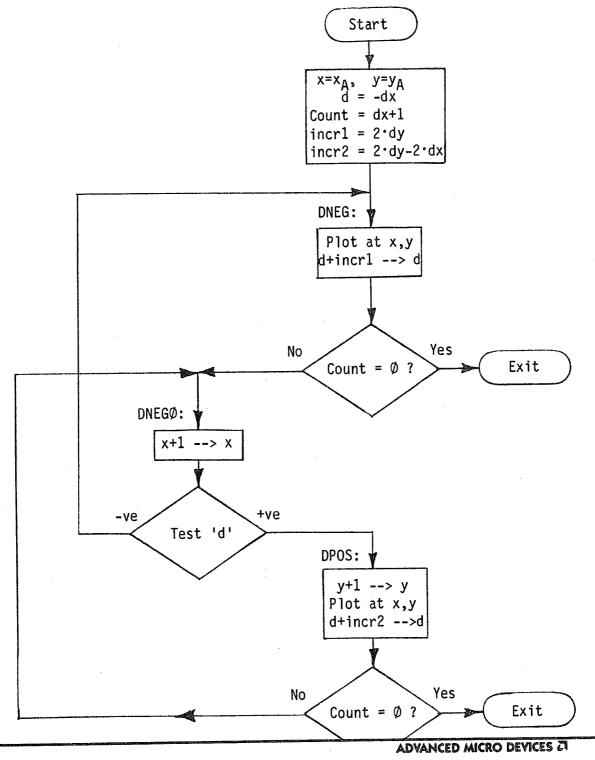

An efficient algorithm for plotting a straight vector from given end points with minimal arithmetic can now be based on the use of a sequence of values of the above discriminant, d. We start with  $x=x_A$ ,  $y=y_A$ ,  $d_1=2\cdot dy-dx$ . For each point we check to see if  $x>x_B$ . If so we terminate the procedure. Otherwise we set the bit corresponding to x,y in the screen memory. Then we check the sign of  $d_i$  and proceed to select the next point and the next discrimininant,  $d_{i+1}$  as follows:

Thus for each point plotted, we require only one addition plus one increment for 'x' and possibly one increment for 'y'. This improved procedure is Bresenham's  $^1$  algorithm for a straight line. Variations on this algorithm can be devised to plot circular and elliptical arcs.

Reference: Bresenham, J.E. "Algorithm for Computer Control of a Digital Plotter" IBM Syst. J., Vol. 4, No. 1 (1965), pp.25-30

#### Am29116 Microcode for Vector Generation

Let us show the code that implements Bresenham's algorithm in two sections. First let us calculate the various quantities needed before the main loop begins.

| We | start | with: | Reg                      | Content              |  |

|----|-------|-------|--------------------------|----------------------|--|

|    |       |       | RØØ<br>RØ1<br>RØ2<br>RØ3 | ×а<br>Уа<br>×в<br>Ув |  |

We want:

| Reg                                    | Content                                                                                         | _            |                  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------|--------------|------------------|--|

| RØØ<br>RØ1<br>RØ2<br>RØ3<br>RØ4<br>ACC | xA<br>yA<br>dx=(pixel count)-1<br>incr1 = 2·dy<br>incr2 = 2·dy-2·dx<br>d <sub>1</sub> = 2·dy-dx | AND SIZE COM | always<br>always |  |

The code required to achieve this result is:

| SOR    | W,MOVE,SORA,RØØ W,SUBS,TORAA,RØ2 W,MOVE,SOAR,RØ2 W,MOVE,SOAR,RØ4 W,MOVE,SORA,RØ1 | & CONT | ; x <sub>A</sub>                    | > ACC                         |

|--------|----------------------------------------------------------------------------------|--------|-------------------------------------|-------------------------------|

| TOR1   |                                                                                  | & CONT | ; dx=x <sub>B</sub> -x <sub>A</sub> | > ACC                         |

| SOR    |                                                                                  | & CONT | ; dx                                | > RØ2 final dx                |

| SOR    |                                                                                  | & CONT | ; dx                                | > RØ4                         |

| SOR    |                                                                                  | & CONT | ; y <sub>A</sub>                    | > ACC                         |

| TOR1   | W,SUBS,TORAA,RØ3                                                                 | & CONT | ; dy=y <sub>B</sub> -y <sub>A</sub> | > ACC                         |

| SHFTNR | W,SHA,SHUPZ,NRA                                                                  | & CONT | ; 2.dy                              | > ACC                         |

| SOR    | W,MOVE,SOAR,RØ3                                                                  | & CONT | ; 2·dy                              | > RØ3 final incr1             |

| TOR1   | W,SUBR,TORAA,RØ2                                                                 | & CONT | ; 2.dy-dx                           | > ACC final d <sub>1</sub> ** |

| TOR1   | W,SUBR,TORAR,RØ4                                                                 | & CONT | ; 2.dy-2.dx                         | > RØ4 final incr2             |

\* Note: "SHFTR" is used to multiply by two.

The alternative of adding RAM to RAM is not available.

\*\* Note: The particular implementation of the main loop we are about to discuss requires that 'd $_1$ ' be adjusted further.

# Am29116 Microcode for Vector Generation (continued)

Program Flow Chart for Main Loop of Bresenham's Vector Algorithm:

## Am29116 Microcode for Vector Generation (continued)

```

The main loop section of the code is as follows:

: -dx --> ACC (final d_1)

TOR1

W.SUBR.TORAA,RØ3

& CONT

; dx+1 \longrightarrow Am291\emptyset counter

W, INC, SORY, RØ2

SOR

& IFNOT CT16 & CT LOW & LDCT JUNK ; Forced pass loads counter

; via "JUMP INDIRECT" path.

LIME &

& OEY

; d is -ve

DNEG:

Instruction #1 of subroutine PLOT ; avoid waste of 1 cycle

YYYY

& IFNOT CT16 & CT LOW & CJS PLOT+1; unconditional CALL

; d+incr1 --> d

TOR

W, ADD, TORAA, RØ3

; Last pt plotted? Jmp if not.

& RPCT DNEGØ

; last point has been plotted

Any instruction

AAAA

& IFNOT CT16 & CT LOW & CJP BRXIT ; unconditional jmp to exit

: x+1 --> x

W, INC, SORR, RØØ

DNEGØ: SOR

; Test sign of d, branch if -ve,

& IF CT16 & CT N & CJP DNEG

: continue if +ve.

; d is +ve

DPOS:

; y+1 --> y

W, INC, SORR, RØ1

SOR

& IFNOT CT16 & CT LOW & CJS PLOT ; unconditional CALL

; d+incr2 --> d

TOR

W,ADD,TORAA,RØ4

: Last pt plotted? Jmp if not.

& RPCT DNEGØ

; The vector is now completely drawn. Exit from Bresenham.

BRXIT: XXXX

; Hardware-dependant routine to plot point at ROO,RO1

PLOT:

First instruction of PLOT subroutine

YYYY

& CONT

Second instruction of PLOT subroutine

PLOT+1:ZZZZ

. . . .

Last instruction of PLOT subroutine

LLLL

```

& IFNOT CT16 & CT LOW & CRTN

; return to caller of PLOT/PLOT+1

### Am29116 Microcode for Vector Generation (continued)

Improving the Vector Algorithm:

The above implementation of Bresenham's algorithm can still be improved. As it stands, the code manipulates the logical addresses, 'x' and 'y', and then plots each point by a procedure ("PLOT") that must convert these address coordinates to physical coordinates. It would be better to work with the physical addresses directly and hence shorten "PLOT".

Suppose the physical address consists of a word address,'W', and a bit address, 'b'. Suppose further that 'b' is represented by a word, 'B', that has a single bit set in the bit position corresponding to 'b'. Then the algorithm can be modified as follows:

1. Replace 'y+1 --> y' by:

W+(# of pixels per line) --> W ... usually add  $2^n$  via 'BOR2 A2NR' ('b' does not need to be altered)

2. Replace 'x+1 --> x' by:

Rotate B up one.

Then if this rotation sets the sign bit, conditionally: 'W+1 --> W'

If the code is altered to manipulate 'W' and 'B' in this manner, then the subroutine, "PLOT", receives the address of the word in the screen memory to be modified, along with the bit bit mask with which to set that word. This shortens "PLOT" by at least 4 cycles. The implementation of this improvement is left as an exercise for the reader.

| · |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

### CHAPTER 5

Intelligent Controllers Based on Am29116

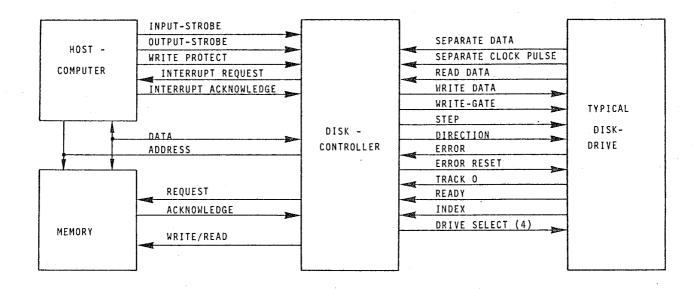

### A Typical Peripheral Controller

BLOCK DIAGRAM OF A TYPICAL PERIPHERAL CONTROLLER

### Peripheral Controllers

The functions of a peripheral controller may include:

- Parallel transmission of data and address information between the host computer and the device being controlled.

- Detection and execution of commands from the host.

- Provision of status information to the host indicating the state of the controller and the controlled device.

- Serial transmission of data to and from the controlled device.

- Generation and testing of status, command and timing bits that coordinate controller/controlled-device interaction.

- Execution of calculations or algorithms related to the control of the peripheral or to processing data from it.

Intelligent Controller

Low Speed Version

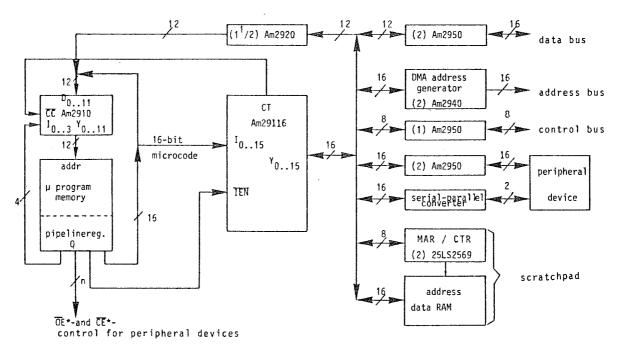

### Intelligent Controller - Low Speed

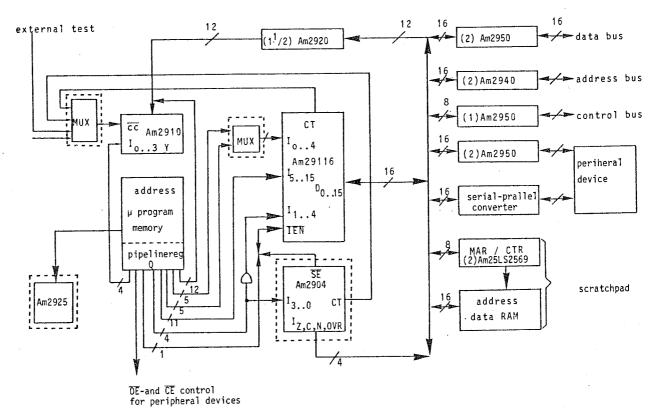

### Devices Needed for the Minimum Configuration:

To control the Am29116:

- Am291Ø sequencer

- Microprogram Memory

- Pipeline Register (could be incorporated in a registered PROM that contains the microprogram)

To control the sequencer:

To interface with the host:

- 2 DMA address generators (Am294Ø's) to drive the host address bus

- $\bullet$  1 bidirectional I/O port (Am295 $\emptyset$ ) interfacing with the host control bus

To interface with the peripheral device:

- $\bullet$  2 bidirectional I/O ports (Am295 $\phi$ 's) conveying status and command signals to and from the peripheral device

- 1 serial-to-parallel converter for the serial data stream to and from the peripheral device

- 1 scratchpad or buffer RAM

And, of course the Am29116

### Low Speed Disk Controller

\*OE = output enable \*CE = clock enable

block diagram of a minimal configuration of a disk controller

### Intelligent Controller - Low Speed

### Brief Description of Some of the Elements

### Am291Ø Sequencer

- an address sequencer intended for controlling the sequence of the execution of microinstructions stored in microprogram memory

- capabilities:

- fixed width of 12 address bits

- simple sequential access

- conditional branching to any microinstruction within its 12-bit  $4\emptyset 96$ -word address range

- incorporates a 12-bit counter for loop control

- provides a 5-level stack for microsubroutine linkage

- can accept an address from one of 4 sources:

- its microprogram address counter

- a direct input from an external source

- its internal register

- its stack

- executes 16 instructions as specified by 4 instruction inputs

- has 5 control pins to control branching, loading of its register, incrementing of its program counter and enabling its output bus drivers

Brief Description of Some of the Elements (continued)

### Am2920 Octal D-Type Flip-Flop

- provides eight edge-triggered D-type flip-flops with

- a buffered common clock

- a buffered common clock enable

- a buffered common asynchronous clear input

- three-state output control

- the clear input, CLR, resets all eight flip-flops independent of all other inputs

- With the three-state output-enable LOW, all eight outputs appear as normal TTL outputs. Otherwise the outputs are in a high impedance state.

- The clock-enable input, E, is used to selectively load data into the register. When E is HIGH the register will retain its current data. When E is LOW, new data is entered on the LOW-to-HIGH transition of the clock input.

Brief Description of Some of the Elements (continued)

### Am295Ø Eight-Bit Bidirectional I/O Port

- designed for use as a parallel data I/O port

- provides 2 back-to-back registers to store data moving in both directions between 2 bidirectional three-state busses

- provides a handshake-flag flip-flop for each data direction to allow coordination of demand-response data transfer:

- Each flag flip-flop is set automatically when a register is loaded.

- Each flag flip-flop has an edge-sensitive clear input.

- provides for each register:

- a clock input

- a clock enable

- a three-state output enable

### Brief Description of Some of the Elements (continued)

### The DMA Address Generator - Am294Ø

- High speed, cascadable, eight-bit wide Direct Memory Access address generator slice

- Generates sequential memory addresses for use in the sequential transfer of data to or from a memory

- Equipped with

- address counter (increment/decrement)

- address register (saves the initial address)

- word counter (increment/decrement)

- word counter register (terminal count)

- three-state address ouput buffers

- 4 control modes

- 8 different instructions (3 instruction pins)

- write/read control register (control mode)

- read word/address counter

- reinitialize counters

- load address/word count

- enable counters

- 3 control pins

Intelligent Controller - Low Speed (continued)

Brief Description of Some of the Elements (continued)

### The Scratch Pad Memory

- Not always necessary for a peripheral controller

- Improves system performance by allowing the host CPU and the peripheral device to respond at different rates.

- May also be useful in improving the execution speed of a controller algorithm by providing quick-access storage for variables or look-up tables. This traffic can thus be kept off of the main bus.

### Microword

- 16 instruction bits for the Am29116 that are shared with the 12 data bits to the Am2910 that provide for loading the counter and providing branch addresses

- 1 bit to determine the destination of the above lines (to either the Am29116 or the Am2910). Use the IEN input of the Am29116 to disable it on those microcycles when the data on the instruction lines is intended for the Am2910.

- 4 instruction bits for the Am291Ø

- 3 instruction bits for the Am2940

- Using this technique of sharing microinstruction fields,

a microword of 28 bits is possible. Of course, there is

a speed penalty caused by the need to halt the Am29116

when data is passed to the sequencer.

### Peripheral Controller with Maximal Performance

block diagram of a maximal configuration of a disk controller

### Additional Elements

- 2 multiplexers:

- to define different Am29116 source and destination registers

- to select the branch condition for the Am291 $\emptyset$

- Am2925 clock generator and microcycle length controller. For extended timing required by Am29116 two-address operation.

- ⊕ Am29Ø4 status and shift control unit:

- to add more flexibility to the Am29116 status tests

- use only the Am29 $\phi$ 4 micro status register and its condition code instructions

### Brief Description of the Additional Elements

### Am2925 Clock Generator and Microcycle Length Controller

- General purpose crystal-controlled clock generator/driver

- Has a microprogrammable clock cycle length:

- provides significant speed-up over fixed clock cycle

- meets a variety of system speed requirements

- Generates four different simultaneous clock output waveforms

- One of eight cycle lengths can be selected by the microprogram

- System control functions include:

- run

- halt

- single-step

- initialize

- ready/wait

- inputs can determine: where a halt occurs

- the end point timing of wait cycles

- Up to 12 pins can be controlled by the microword.

### Brief Description of the Additional Elements (continued)

### Am2904 Status and Shift Control Unit

- Designed to perform all the miscellaneous functions which are usually performed in MSI around an ALU

- It contains three nearly independent blocks of logic:

- multiplexer to generate the carry-in

- 4 three-state multiplexers for shift linkage

- 2 status registers for storing carry, overflow, zero and negative status flags.

These status registers control a condition-test output via a condition code multiplexer.

A wide selection of condition-code test logic is provided.

In our application only the status registers and condition-test logic is used.

### Brief Description of the Additional Elements (continued)

### Am29Ø4 Condition Code Output

| $I_3 - I_\emptyset$ | Condition                         | Code | Output |

|---------------------|-----------------------------------|------|--------|

| Ø Ø Ø Ø             | (N⊕OVR)+Z                         |      |        |

| Ø Ø Ø 1             | (N@OVR)·Z                         | *    |        |

| Ø Ø 1 Ø             | N⊕OVR                             |      |        |

| Ø Ø 1 1             | N@OVR                             | *    |        |

| Ø 1 Ø Ø             | Z                                 |      |        |

| Ø 1 Ø 1             | Z                                 | *    |        |

| Ø 1 1 Ø             | OVR                               |      |        |

| Ø 1 1 1             | OVR                               | *    |        |

| 1 Ø Ø Ø             | C+Z                               | *    |        |

| 1 Ø Ø 1             | $\overline{C} \cdot \overline{Z}$ | *    |        |

| 1 Ø 1 Ø             | С                                 |      |        |

| 1 Ø 1 1             | C                                 | *    |        |

| 1 1 Ø Ø             | <del>C</del> +Z                   |      |        |

| 1 1 Ø 1             | $C+\overline{Z}$                  | *    |        |

| 1 1 1 Ø             | N                                 |      |        |

| 1 1 1 1             | $\overline{N}$                    | *    |        |

<sup>\* 9</sup> Condition codes  $\underline{\text{not}}$  available at the Am29116 CT-output.

### Reasons for the Better Performance of the Second Solution

- $\bullet$  Instruction inputs of the Am29116 and the  ${\rm D}_{\emptyset-11}$  inputs of the Am2910 are driven from separate microcode bits.

- allows simultaneous instruction execution in the Am29116 and direct-address branching in the Am291 $\phi$

- requires an additional 12 bits in the microinstruction

- Multiplexer at the CC-input of the Am291Ø (controlled by 2 bits)

- allows testing of conditions without loading the signals into the  $\mbox{Am}\mbox{29116}$

- $\bullet$  T<sub>1-4</sub> inputs of the Am29116 driven by 4 additional microword bits

- allows simultaneous testing and execution of an Am29116 instruction

- Use of the Am2904 (controlled by 4 bits)

- improved flexibility in status testing

- Multiplexer at the  $I_{0-4}$  inputs of the Am29116 (needs 6 bits)

- allows different source and destination addresses in RAM in the same microcycle

- The Am2925 clock generator/driver

- able to dynamically alter the length of the microcycle

$\label{ligent Controller} Intelligent \ Controller \\$  Comparison with an Am2901 - Based Solution

Alternate Means of Obtaining Am29116 Features

| Am2901-Based Solution | Use 4 Am2901 microprocessor slices and<br>1 Am2902 carry-look-ahead generator. | Am2901 has 16 registers but is not readily expandable. For additional registers use Am2903 or Am29203 processor with 4 Am2970516 x 4-bit register file extenders. |

|-----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <b>⊗</b>                                                                       | <b>⊗</b>                                                                                                                                                          |

| Am29116               | 16-bit data path                                                               | 32 registers                                                                                                                                                      |

White is a second of the se

16-bit barrel shifter

# Alternate Means of Obtaining Am29116 Features (continued)

| ی  | ) |

|----|---|

| _  | 4 |

| _  | 4 |

| σ  | 1 |

| `` | J |

| Δ  | Ξ |

| 9  | ( |

|    |   |

## Am2901-Based Solution

- Status register and condition code generator/MUX

- Use 2 Am2904 status and shift control units

- One Am2904 for the ALU flags (C,N,OVR,Z) and condition code generation

- One Am2904 for the 3 user-definable flags and the linkage flag

### Byte/Word Mode

- Use two output enable bits  $(\overline{0E_{\gamma}})$ . Then in byte operations force  $\overline{0E_{\gamma}}$  high for slices 3 and 4.

- Multiplex status lines at slices 2 and 4

## Note: This will permit external byte-mode functions. Operations on internal registers will still alter all 16-bits. You should choose Am29203 rather than Am2901 if Byte/Word operations are important. When used with a status-flag MUX, Am29203 fully supports Byte/Word operations.

Alternate Means of Obtaining Am29116 Features (continued)

| Built-in 16-bit priority encoder<br>Masking capability of the ALU |

|-------------------------------------------------------------------|

|                                                                   |

### Am2901-Based Solution

- mask the first operand

Use two 8-bit Am25LS2513 priority encoders Use three microcycles:

- mask the second operand

- operate on the masked operands

Bit oriented instructions

CRC instructions

Can be emulated by a lengthy microcode sequence. Will execute too slowly for many applications.

Emulate with several microinstructions

### Intelligent Controller - Using Am2901

### Brief Description of the Additional Devices

### Am29Ø1 4-bit Microprocessor Slice

- High-speed cascadable element for use in

- CPU's

- peripheral controllers

- programmable microprocessors

- numerous other applications

- Consists of:

- a 16-word by 4-bit two-port RAM

- a high-speed 8-function ALU

plus shifting, decoding and multiplexing sections

- Cascadable with either:

- simple ripple carry propagation

- the Am29Ø2 look-ahead carry generator

- Produces 4 status flags (N, OVR, C, Z)

- accepts 9-bit microinstructions:

- 3 bits select the ALU operand source

- 3 bits select the ALU function

- 3 bits select the ALU destination

- accepts 8 bits to select the two RAM addresses

- $\bullet$  accepts 2 control bits ( $\overline{OE}$  and carry-in)

5-18Ø

### Intelligent Controller - Using Am29Ø1

### Brief Description of the Additional Devices

### Am2902 High-Speed Look-Ahead Carry Generator

- Provides anticipated carries across a group of four binary ALU's

- Accepts up to 4 pairs of carry Propagate and carry Generate signals from an ALU and one carry input.

With ALU operands A and B and an addition operation:

$$P = \overline{P_3 \cdot P_2 \cdot P_1 \cdot P_\emptyset} \quad G = \overline{G_3 + P_3 \cdot G_2 + P_3 \cdot P_2 \cdot G_1 + P_3 \cdot P_2 \cdot P_1 \cdot G_\emptyset}$$

$$P_\emptyset = A_\emptyset + B_\emptyset \qquad G_\emptyset = A_\emptyset \cdot B_\emptyset$$

$$P_1 = A_1 + B_1 \qquad G_1 = A_1 \cdot B_1$$

$$P_2 = A_2 + B_2 \qquad G_2 = A_2 \cdot B_2$$

$$P_3 = A_3 + B_3 \qquad G_3 = A_3 \cdot B_3$$

- Also provides carry-propagate and carry-generate signals to use for further levels of look-ahead.

- Logic results provided at the outputs are:

$$C_{n+x} = \overline{G_{\emptyset} + P_{\emptyset} \cdot C_{n}}$$

$$C_{n+y} = \overline{G_{1} + P_{1} \cdot G_{\emptyset} + P_{1} \cdot P_{\emptyset} \cdot C_{n}}$$

$$C_{n+z} = \overline{G_{2} + P_{2} \cdot G_{1} + P_{2} \cdot P_{1} \cdot G_{\emptyset} + P_{2} \cdot P_{1} \cdot P_{\emptyset} \cdot C_{n}}$$

$$\overline{G} = G_{3} + P_{3} \cdot G_{2} + P_{3} \cdot P_{2} \cdot G_{1} + P_{3} \cdot P_{2} \cdot P_{1} \cdot G_{\emptyset}$$

$$\overline{P} = P_{3} \cdot P_{2} \cdot P_{1} \cdot P_{\emptyset}$$

### Intelligent Controller - Using Am29Ø1

### Brief Description of the Additional Devices

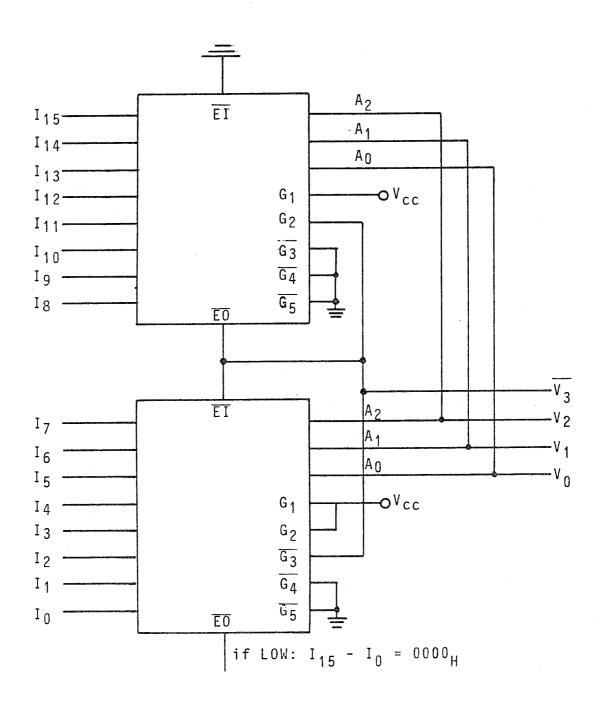

### Am25LS2513 Three-State Priority Encoder

- Encodes eight lines to three-line binary

- Three-state outputs

- controlled by three active LOW and two active HIGH inputs

- Cascadable

- provides an input enable and an output enable to permit cascading without additional circuitry

### Building a 16-bit Priority Encoder from 2 AM25LS2513

Intelligent Controller - Using Am29Ø1

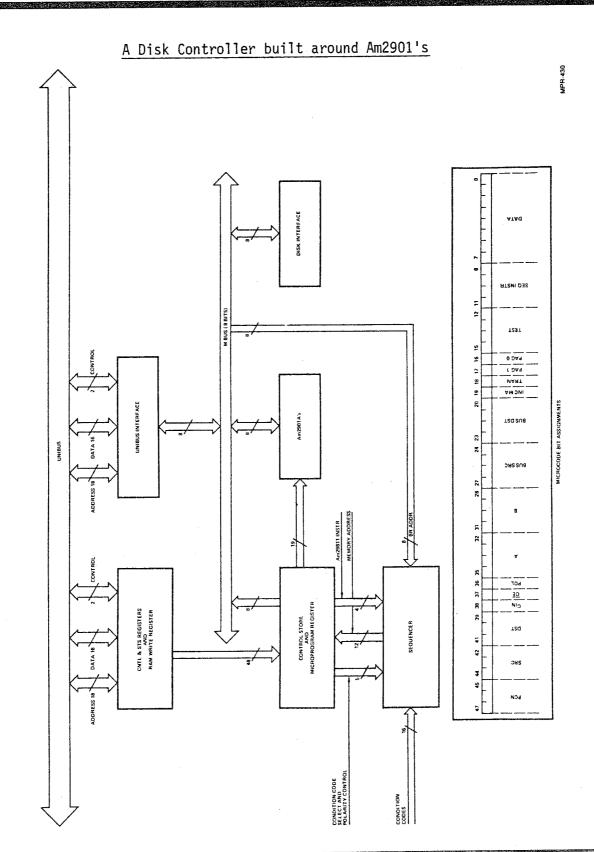

Thus we have seen that it is rather hard to build a controller with the same features as the AM29116 from parts with a lower level of integration.

On the next page we see a simple disk controller based on a pair of Am29Ø1A's.

### The Microword for the 2901 - Based Solution

- 48 bits wide

- . 19 bits Am2901 instruction (M47 M37, M35 M28)

- 3 bits function select (FCN)

- 3 bits source (SRC)

- 3 bits destination (DST)

- 4 bits A port register address

- 4 bits B port register address

- 1 bit carry in  $(C_N)$

- 1 bit output enable (OE)

- 8 bits M-bus control (M27 M20)

- 4 bits bus source (BUS SRC)

- 4 bits bus destination (BUS DST)

- . 11 bits sequencer (M36, M17 M8)

- 4 bits Am2911 instruction (SEQ INSTR)

- 4 bits condition code select (TEST)

- 1 bit polarity of CC (POL)

- 2 bits to determine the page of microprogram memory

- . 8 bits data (M7 M0)

- . 2 bits additional control (M19, M18)

- 1 bit increments MAR (INC MA)

- 1 bit initiate data transfer (TRAN)

Intelligent Controller

Very High Speed Solution

## Intelligent Controller - Very High Speed

### Some General Considerations

- Interface-signal names, polarities and functions used here are similar to those used in the current ANSI standard for hard-disk drives.

- The methods and functions discussed here can be used for most current hard- or flexible-disk drives.

- With minimal external logic, this controller uses an Am29116 and an Am952Ø burst error processor to perform all of the functions needed to:

- write and read at 30 Mbits per second

- format a disk

#### Including:

- searching a track for a specific header and sector

- managing data flow through a high-speed buffer memory

- generating modified Fire-code check bits while writing

- detecting and correcting single and burst errors on reading

- generating and checking of CRC's in sector headers

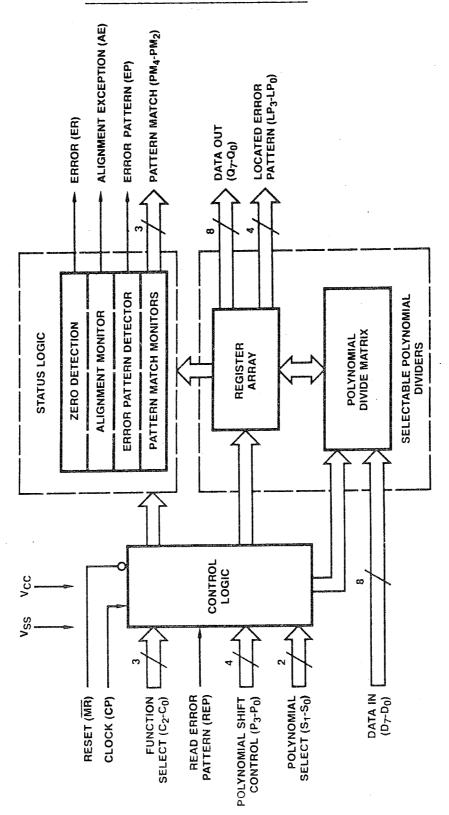

#### Am952Ø Burst Error Processor

#### Distinctive Characteristics:

- Provides for detection and correction of burst errors:

- detects errors in serial-data blocks up to 585K bits long

- allows correction of error bursts of up to 12 bits long

- Effective data rates up to 20 Mbits per second:

- fast enough for high-performance hard disk systems

- Four selectable industry-standard polynomials:

- popular IBM 56- and 48-bit polynomials

- also 35-bit and 32-bit polynomials

- Three correction algorithms provide flexibility:

- full-period clock-around method compatible with current practice

- Chinese Remainder Theorem method reduces correction time by orders of magnitude

- reciprocal polynomial method for correction with the 48-bit IBM code

- Designed for use in disk controllers and communication systems based on fixed-instruction-set or microprogrammed processors.

## Am9520 Burst Error Processor

# Am9520 Burst Error Processor (continued)

Functional Description:

- Register Array

- consists of 56 flip-flops used for

- . check-bit computation during write operations

- . syndrome computation during read operations

- . error pattern extraction during error correction operations

- Polynomial-Divide Matrix:

- establishes interconnections and feedback for a group of shift registers such that an entire byte of data is divided in a parallel operation by the selected polynomial

- the matrix is controlled by 2 Polynomial Select and 2 Function Select inputs

- the data is presented to the matrix a byte at a time on 8 data lines

- When correction operations are complete, the error pattern is available on 12 outputs:

- eight bits on the  $\mathbf{Q}_{\emptyset}\text{-}\mathbf{Q}_{7}$  outputs

- four bits on the  $\mathsf{LP}_{\emptyset}\text{-}\mathsf{LP}_3$  outputs

# Am9520 Burst Error Processor (continued)

#### a Write:

- While the data is being written, the Am9520 is in the Compute-Check-Bits mode, calculating the polynomial remainder without affecting the flow of data to the disk

- After the last data byte, the Am952Ø is switched into the Write-Check-Bits mode, outputting the 4, 5, 6 or 7 check bytes.

- These check bytes constitute additional information to be appended to the data stream to allow detection and correction of errors on reading.

#### Read:

- Two modes are available when reading: Normal and High Speed

- The two modes use different correction algorithms.

- After the last information byte has been read, the state of the ER output signal indicates whether an error has occured.

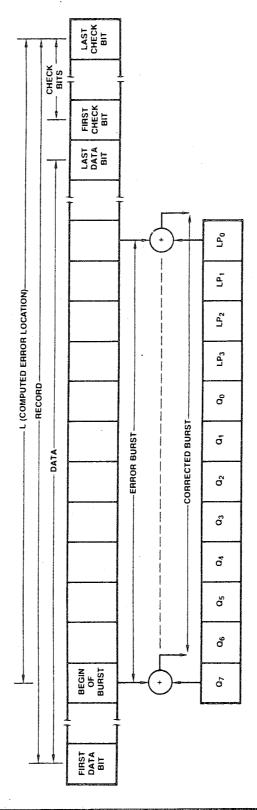

### Am952Ø Burst Error Processor (continued)

#### © Correction:

- After the read operation, the syndrome in the register array contains information specifying:

- · the location of the error

- · the bit pattern of the error

#### Normal Correction Mode:

- The error location is found by counting the number of clock pulses required to make the EP output go HIGH.

- The error pattern available on  $LP_{\emptyset}-LP_{3}$  and  $Q_{\emptyset}-Q_{7}$  can be Exclusive ORed with the data to effect the correction.

#### High-Speed Correction Mode:

- The error location is found by counting the number of clock pulses required to generate an indicator for each of the 2 or 4 factors of the polynomial.

- The error pattern available on  $LP_0-LP_3$  and  $Q_0-Q_7$  can be Exclusive ORed with the data to effect the correction.

- While there are more steps to the high-speed-correction procedure than are required by the "Normal" procedure, the correction is accomplished far faster.

- The high-speed correction method is not available for the 48-bit polynomial.

- For the 56-, 35- and 32-bit polynomials, the high-speed method should be preferred over the "normal method".

### Am952Ø Burst Error Processor (continued)

Computing Check Bits:

- The Polynomial Divide Matrix and the Register Array implement the familiar serial form of feedback shift register arrangement in an 8-bit parallel form.

- $\bullet$  The S<sub>1</sub> and S<sub>0</sub> inputs select one of 4 polynomials:

| Polynomial                                               | Degree &<br>Number of<br>Check Bits | Period<br>(Bits)                                   | Correctable<br>Burst Error<br>Length (Bits) |

|----------------------------------------------------------|-------------------------------------|----------------------------------------------------|---------------------------------------------|

|                                                          | 56                                  | 585,442                                            | 11                                          |

| $(x^{21}+1) \cdot (x^{11}+x^2+1)$                        | 32                                  | 42,987                                             | 11                                          |

| $(x^{23+1}) \cdot (x^{12}+x^{11}+x^{8}+x^{7}+x^{3}+x+1)$ | 35                                  | 94,185                                             | 12                                          |

| $(x^{13}+1) \cdot (x^{35}+x^{23}+x^8+x^2+1)$             | 48                                  | 13·(2 <sup>35</sup> -1)<br>=4.466x1Ø <sup>11</sup> | 7                                           |

- When the last data byte has been read or written, the Register Array contains the check bits.

- Remember to select the same polynomial for reading as was used for writing.

Am9520 Burst Error Processor (continued)

Computing Check Bits (continued)

- Sequence of events to compute the check bits

- i) The clock input, CP, should be in the quiescent HIGH state.

- ii) Initialize by activating the master reset input,  $\overline{\text{MR}}$ , LOW and return it to HIGH.

- iii) Specify the desired polynomial via  $S_{0}$  ,  $S_{1}$  . Apply zeroes to  $c_{2}\text{-}c_{0}$  to select Compute-Check-Bits mode.

- iv) Establish a byte of data on  $D_0-D_7$  inputs.

- v) Make the clock input go LOW then HIGH.

- vi) Repeat from step iv) until all data bytes are entered.

# Am952Ø Burst Error Processor (continued)

#### Write Check Bits:

- When the Write-Check-Bits mode is established, the feedback paths of the register array are disabled and the check bits may be shifted out.

- ullet Checkbits are available on the  ${\bf Q}_{oldsymbol{Q}}{oldsymbol{-}}{\bf Q}_{7}$  outputs one byte at a time.

- Sequence of events to obtain the check bits:

- i) The clock input, CP, should be in the quiescent HIGH state.

- ii) Select the polynomial via the  $S_{\emptyset}, S_1$  inputs.

- iii) Force  $C_2, C_1, C_\emptyset$  to LOW LOW HIGH (Write Check Bits).

- iv) After a propagation delay the  ${\rm Q}_{0}\text{-}{\rm Q}_{7}$  outputs will contain the first check byte.

- v) Make the clock input go LOW then HIGH. The next check byte will be available on the  ${\rm Q}_0\text{-}{\rm Q}_7$  outputs.

- vi) Repeat from step v) until all check bytes are read out.

### Am952Ø Burst Error Processor (continued)

#### Read - General:

- The input stream (data and check bytes) is divided by the selected polynomial to obtain the syndrome.

- A non-zero syndrome indicates an error has been detected. If the syndrome is not zero the ER output will be HIGH.

- Two methods for error correction are available:

- full-period clock-around ("Normal")

- Chinese Remainder Theorem ("High Speed Method")

- There is a different read procedure for each of these methods:

- Read Normal: produces one syndrome

- Read High Speed: produces as many syndromes as the number of factors in the polynomial.

The input stream is simultaneously divided by all of the factors of the polynomial. The ER output indicates whether or not all syndromes are zero.

• Read High Speed is not available for the 48-bit polynomial

# Am9520 Burst Error Processor (continued)

#### Read Normal:

- Sequence of events for Read Normal:

- i) The clock input should be in the quiescent HIGH state.

- ii) Initialize by pulling the master reset,  $\overline{\text{MR}}$ , LOW and then returning it to HIGH.

- iii) Select the required polynomial via  $S_\emptyset, S_1$  inputs.

- iv) Apply LHL to  $C_2, C_1, C_0$  to select Read Normal.

- v) Present a byte of information as read from the disk to the  $D_{0}\text{-}D_{7}$  inputs.

- vi) Make the clock go LOW then HIGH.

- vii) Repeat from step v) until the last check byte read from the disk is processed.

- viii) Test the ER output:

- ER HIGH: an error has been detected.

- ER LOW: no error has been detected.

### Am9520 Burst Error Processor (continued)

#### High Speed Read:

- Sequence of events for Read High Speed:

- i) The clock input, CP, should be in the quiescent HIGH state.

- ii) Specify the polynomial via the  $S_{\mathcal{O}}, S_1$  inputs.

- iii) Apply LHH to  $C_2,C_1,C_\emptyset$  to select Read High Speed.

- iv) Initialize by pulling the master reset, MR, LOW and then returning it to HIGH.

- v) Present a byte as read from the disk to the  $D_0-D_7$  inputs.

- vi) Make the clock go LOW then HIGH.

- vii) Repeat from step v) until the last check byte has been read.

- viii) Test the ER output:

- ER HIGH: an error has been detected.

- ER LOW: no error has been detected.

# Am952Ø Burst Error Processor (continued)

#### Function Select Codes

| C <sub>2</sub> | $c_1$ | СØ | Function           |

|----------------|-------|----|--------------------|

| L              | L     | L  | Compute check bits |

| L              | L     | Н  | Write check bits   |

| L              | Н     | L  | Read normal        |

| L              | Н     | Н  | Read high speed    |

| Н              | L     | L  | Load               |

| Н              | L     | Н  | Reserved           |

| Н              | Н     | L  | Correct normal     |

| Н              | Н     | Н  | Correct high speed |

#### Am952Ø Burst Error Processor (continued)

#### Correct Normal:

- The Am952∅ manipulates the syndrome to yield:

- error pattern (at  $Q_0$ - $Q_7$  and  $LP_0$ - $LP_3$  outputs)

- error location (needs further external computation)

- Syndrome is repeatedly divided by the polynomial until the error pattern is located:

- done by repeatedly clocking without regard to the  $\rm D_{0}\text{-}D_{7}$  inputs until EP goes HIGH

- If the AE output goes HIGH while the EP output remains LOW, an alignment exception has been detected.

- Count clock cycles (#C) until EP goes HIGH.

- If #C > (period of polynomial) then the error is uncorrectable.

# Am952Ø Burst Error Processor (continued)

Correct Normal: (continued)

- Use two external counters (R1, R2)

- R1 counts the number of cycles until AE goes HIGH

- R2 counts the number of cycles from AE going HIGH to EP going HIGH. (=  $\emptyset$  if no alignment exception)

- If R1+R2 > (period of polynomial) then the error is uncorrectable.

- (N·K 8·R1 R2) gives the location of the first bit in the error burst counting from the last check bit of the record for the 56-bit and 32-bit polynomials.

(N·K -  $8\cdot$ R1 - R2+5) gives the location of the first bit in the error burst counting from the last check bit of the record for the 35-bit polynomial.

#### where:

K is the smallest +ve integer that makes this expression +ve. and N is the period of the polynomial.

Note: The 48-bit polynomial uses another correction algorithm. See specification sheet for details.

### Am952Ø Burst Error Processor (continued)

Burst Error Processor (continued)

Correct High Speed:

- This mode allows you to determine the error pattern in far fewer clock cycles than does the "Normal" mode.

- A polynomial with m factors with periods  $P_1, P_2, \ldots, P_m$  will correct in no more than the following number of of clock cycles:

- . In Normal mode:  $P_1 \cdot P_2 \cdot \ldots \cdot P_m$  i.e. the product of the P's

- . In High Speed mode:  $P_1+P_2+ \dots +P_m$  i.e. the sum of the P's

- Number of syndromes equals the number of factors of the polynomial.

- Refer to the table a few pages back which shows the factorization of the polynomials.

As we have written the factors, the first factor has a special signifigance. The degree of this first factor determines the maximum length of an error burst that is still correctable.

# Am9520 Burst Error Processor (continued)

• The error location is given by:

$$L = N \cdot K - (A1M1 + A2M2 + ... + A_m M_m)$$

Where N is the natural period of the polynomial. K is the smallest integer that makes L positive.  $M_i$  are the numbers of clock cycles required to match the error pattern of each factor. and  $A_i$  are the Chinese Remainder Theorem coefficients:

| Polynomials | A1      | A2               | А3        | A4        |

|-------------|---------|------------------|-----------|-----------|

| 56-bit      | 452,387 | 578,864          | 2,521,904 | 2,647,216 |

| 32-bit      | 311,144 | 32 <b>,</b> 76Ø  | <b></b>   |           |

| 35-bit      | 32,760  | 72Ø <b>,</b> 728 |           | an 400    |

# Am952Ø Burst Error Processor (continued)

Correct High Speed (continued)

- To determine M<sub>i</sub> and the error pattern use:

- $P_0-P_3$  inputs to select the register section to be clocked

- PM<sub>2</sub>-PM<sub>4</sub>, the "pattern match" outputs:

When PM<sub>i</sub> is HIGH then the syndrome<sub>i</sub> shows a match with the error pattern.

- For M1: use the polynomial-shift controls to select register-section #1 ( $P_0$ , $P_1$ , $P_2$ , $P_3$  HLLL).

Use the same procedure as in the correct normal mode.

- If R1+R2 > (period of factor #1) then error is uncorrectable.

- If error is correctable then M1 = 8R1 + R2

- ullet The M $_{

m i}$  will be determined after M1 but slightly differently:

- Select the i<sup>th</sup> register section via  $P_3$ - $P_{\emptyset}$

- While  $\mathrm{PM}_{\mathrm{i}}$  is LOW clock the 9520 and increment a counter

- If the count exceeds the period of this factor the error is not correctable.

- $\ensuremath{\text{e}}$  When EP and all PM  $_{\ensuremath{\text{j}}}$  's associated with this polynomial are HIGH, then the error pattern and error location are determined.

# Am952Ø Burst Error Processor (continued)

# Am952Ø Polynomial Periods

| Polynomial | Period<br>Factor 1 | Period<br>Factor 2 | Period<br>Factor 3 | Period<br>Factor 4 | Composite<br>Period (N) |  |  |

|------------|--------------------|--------------------|--------------------|--------------------|-------------------------|--|--|

| 56-bit     | 22                 | 13                 | 89                 | 23                 | 585,442                 |  |  |

| 32-bit     | 21                 | 2Ø47               |                    | age pic            | 42,987                  |  |  |

| 35-bit     | 23                 | 4Ø95               |                    |                    | 94,185                  |  |  |

Note: The 48-bit polynomial requires the use of a different correction procedure and is not shown here.

Error Pattern Format for 56-Bit, 35-Bit and 32-Bit Polynomials

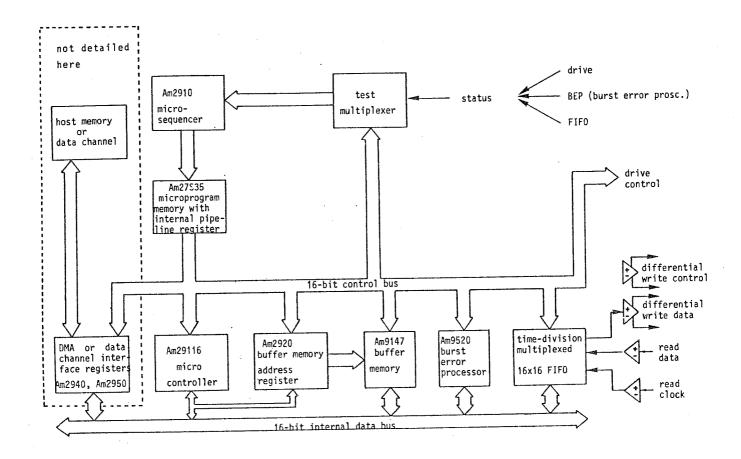

# Data Path for Very High Speed Controller

### System Organisation:

- Interface to the disk drives:

- bit-serial data paths for read and write

- byte-parallel paths for

- . commands

- . disk addresses

- . disk status

- ♠ Am291Ø sequencer and Am27S35 registered PROM microprogram memory drives 76-bit control bus:

- Data flow is:

- asynchronous & serial at 30 Mbits/sec from drive to a FIFO array

- 16-bit clocked & parallel from the FIFO array to the buffer memory at 20 Mbits per second via the internal data bus.

- The BEP is located on the internal data bus.

- Disk read:

- Data is read into the FIFO array at 30 Mbit per second.

- Concurrently, the data is transferred from the buffer memory to the BEP at a rate of 15 MHz.

- a Disk write:

- The BEP pre-calculates the check bits before the write. There is not enough time to overlap BEP/buffer and buffer/FIFO transfers.

# Microinstruction Format

- 8Ø-bit wide microinstruction

- This is not a minimum width, but it demonstrates microcoding in a straightforward manner.

- Sample microcode for uncompressed sector read/write operations is available including:

- header and sector searching

- error checking of the header via Am29116 CRC instructions

- error checking and correction of the data segments

via Am952Ø and its 56-bit modified Fire code polynomial

- The sector input/output microroutine (SECTIO) performs input or output of a single 256-byte sector.

Microinstruction for the Very High Speed Controller

Microinstruction Field

| Bits  | Width       | Mnemonic                 | Comment                                                                                           |

|-------|-------------|--------------------------|---------------------------------------------------------------------------------------------------|

| 79-64 | 16          | $I15-I\emptyset$         | Am29116 Instruction                                                                               |

| 63-60 | 4           | T4-T1                    | Am29116 Conditional Test Select                                                                   |

| 59    | 1           | SRE                      | Am29116 Status Register Enable                                                                    |

| 28    | Н           | $\overline{0E_{\gamma}}$ | Am29116 Output Enable Y-Bus                                                                       |

| 22    | П           | IEN                      | Am29116 Instruction Enable                                                                        |

| 26    | -           | DLE                      | Am29116 Data Latch Enable                                                                         |

| 55-52 | な           | Ø1−E1                    | Am2910 Instruction                                                                                |

| 51-42 | 10          | D9-DØ                    | Am2910 Direct Input                                                                               |

| 41-36 | 9           | !                        | Condition-Code MUX Selection & Polarity                                                           |

| 35    | ⊣           | ADMC                     | Address Mark Control                                                                              |

| 34    | 1           | BFCB                     | (Enable Memory) Bus from (Disk Drive) Control Bus                                                 |

| 33    | <del></del> | <u>BFTP</u>              | (Enable Memory) Bus from Translate PROM<br>(Translate PROM needed in data compression operations) |

| 32    | Н           | BFØ3                     | (Enable Memory) Bus from 9403A FIFO array                                                         |

Microinstruction for the Very High Speed Controller (continued)

Microinstruction Field

| Comment  | (Enable Memory) Bus from Am29116 Y-Bus | (Enable Memory) Bus Lower Byte from Am9520 Q-Bus | (Enable Memory) Bus Upper Byte from Am9520 Q-Bus | Bus Direction OUT | (Enable Memory) Bus to 9403A FIFO Array | (Enable Memory) Bus to Am29116 Y-Bus | (Enable Memory) Bus Lower Byte to Am9520 D-Bus | (Enable Memory) Bus Upper Byte to Am9520 D-Bus | (Enable Memory) Bus to Am9520 REP, P3-P0, C2-C0 | Clock Enable Am9520 to Lower-Byte Bus Interface Register | Clock Enable Memory Bus to Am952Ø Interface Registers | Clock Pulse for 9520 (Microcoded Waveform) | Command Request | (Enable Serial Data) Input to 9403A FIFO Array |

|----------|----------------------------------------|--------------------------------------------------|--------------------------------------------------|-------------------|-----------------------------------------|--------------------------------------|------------------------------------------------|------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|-----------------|------------------------------------------------|

| Mnemonic | BF16 (                                 | BF2L (                                           | <u>BF2U</u> (                                    | BOUT B            | <u>BTØ3</u> (                           | BT16 (                               | BT2L (                                         | <u>BT2U</u> (                                  | 8720                                            | CE2L (                                                   | <u>CE20</u>                                           | <u>CP20</u>                                | CREQ            | INPT                                           |

| Width    | , <del>, -1</del>                      | П                                                | Н                                                | <del>, −</del> −1 | <del>-  </del>                          | П                                    | 1                                              | H                                              | Н                                               | ⊣                                                        | Н                                                     | ,<br>,1                                    | ·               | 1                                              |

| Bits     | 31                                     | 30                                               | 29                                               | 28                | 27                                      | 56                                   | 25                                             | 24                                             | 23                                              | 22                                                       | 21                                                    | 20                                         | 19              | 18                                             |

Microinstruction for the Very High Speed Controller (continued)

Microinstruction Field

| Comment  | (Enable) Jump Indirect Am29116 Y-Bus (double rail) | (Enable Loading of Buffer) Memory Address Register | (Enable Buffer) Memory Read | (Enable) Memory Write Operation | (Enable Serial Data) Output from 9403A FIFO array | Parameter Enable | (Enable Setting of Am9520) P Bits from Am9520 PM Bits | (Enable) Parallel Fetch from 9403A FIFO array | (Enable) Parallel Load of 9403A FIFO array | Parameter Request | Read Gate | Reset 9403A FIFO array | Select/Attention Strobe | Write Gate   | Translate Table Select for Data Compression PROM |

|----------|----------------------------------------------------|----------------------------------------------------|-----------------------------|---------------------------------|---------------------------------------------------|------------------|-------------------------------------------------------|-----------------------------------------------|--------------------------------------------|-------------------|-----------|------------------------|-------------------------|--------------|--------------------------------------------------|

| Mnemonic | JMPI                                               | MADR                                               | MREA                        | MWRT                            | 00PT                                              | PENB             | PFPM                                                  | PFØ3                                          | PLØ3                                       | PREQ              | RDGA      | RFIF                   | SAST                    | WRGA         | XLAT                                             |

| Width    | 2                                                  | Н                                                  | П                           | <b>-</b>                        | П                                                 |                  | 1                                                     | <b>.</b> Н                                    | П                                          | ᡊ                 | ⊷         | ᆏ                      | <del></del> 1           | <del>,</del> | က                                                |

| Bits     | 17-16                                              | 15                                                 | 14                          | 13                              | 12                                                | 11               | 10                                                    | 6                                             | 8                                          | 7                 | 9         | 22                     | 4                       | က            | 2-0                                              |

#### Conclusion

What makes this controller so fast?

- The Am29116 microprocessor has been combined with the Am952∅ burst error processor.

- This provides the powerful Am29116 instruction set and the very effective hardware elements of the Am29116:

- . its CRC logic

- . 32 registers

- . barrel shifter

- . priority encoder

- The Am952 $\emptyset$  is a relevant specialized device which:

- . generates the checksum

- . checks the data together with the checksum and produces both the error pattern and error location

- . is very fast (due to its special hardware).

You can calculate a CRC remainder -

on an Am9520 at 50nsec per data byte. on an Am29116 at 200nsec per data bit.

(The Am952 $\emptyset$  is 32x faster than the Am29116!).

■ The Am952Ø is unique in supporting the very fast Chinese Remainder Theorem method that greatly speeds the correction of a faulty sector.

This method is fully supported by hardware for use while reading and in the correction calculation itself.

# Conclusion (continued)

- We can write special microcode: for example for packing ASCII fields. This is not possible with a fixed-instruction-set processor or a specialized LSI disk-controller chip.

- We are making use of the parallel hardware of the 952∅. For example, the Am952∅ can perform up to four simultaneous polynomial division operations and produce four independent syndromes concurrently.

- We are concurrently reading from the disk and generating the polynomial remainders for error detection and correction.

(We were not able to support checkbit calculation in parallel with writing, however).

- $\blacksquare$  We have used a FIFO array to allow us to read a data stream that is faster than even an Am952Ø can check it.

- We have incorporated a buffer memory that:

- holds images of the last eight sectors read from or written to disk

- holds I/ $\phi$  request queues to maximize throughput

- holds additional house keeping tables

- We have used a PROM to translate from EBCDIC data to packed-BCD or ASCII

## CHAPTER 6

Application of Am29116 to General Purpose CPUs

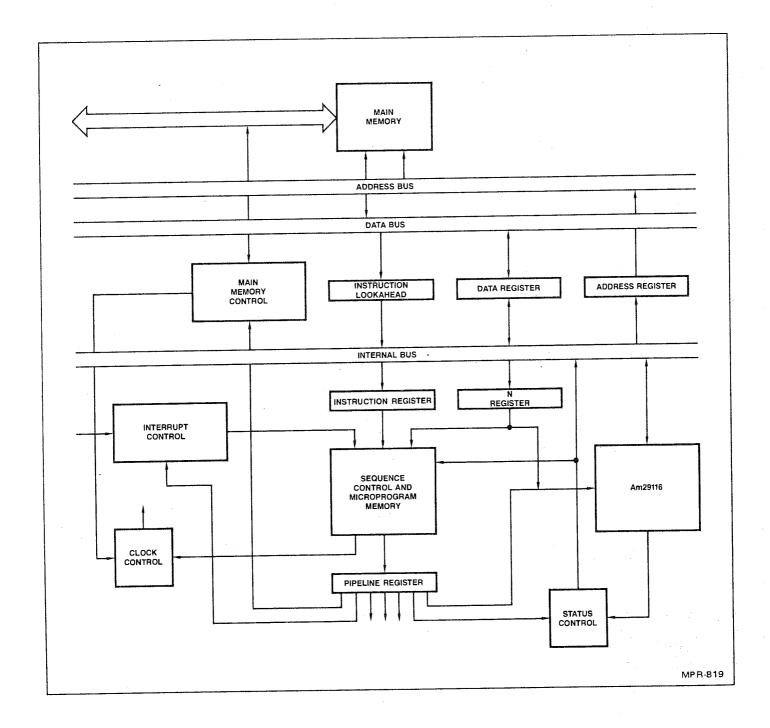

# A Microprogrammed CPU Using Am29116

The following pages provide an introduction to AMD Application Note MPR-1712

# A Microprogrammed CPU Using Am29116

### Introduction and System Overview

- Am29116 is optimized for peripheral controller applications

- However, Am29116 is also an ideal choice for CPU's as well.

- it has a powerful instruction set for:

- . arithmetic operations

- . data movement

- . multiple-bit shifts

- . bit manipulation

- . status manipulation

- it has high speed (100 nsec cycle time)

- it can reduce power requirements

- it save area on PC boards

- We will describe a CPU built with the Am29116 which maintains architectural and software compatibility with the Super-16.\*

- This CPU incorporates pipelining at

- the microprogram level

- the macroinstruction level

- \* As described in detail in "Bitslice Microprocessor Design" by Mick and Brick, Chapter 9

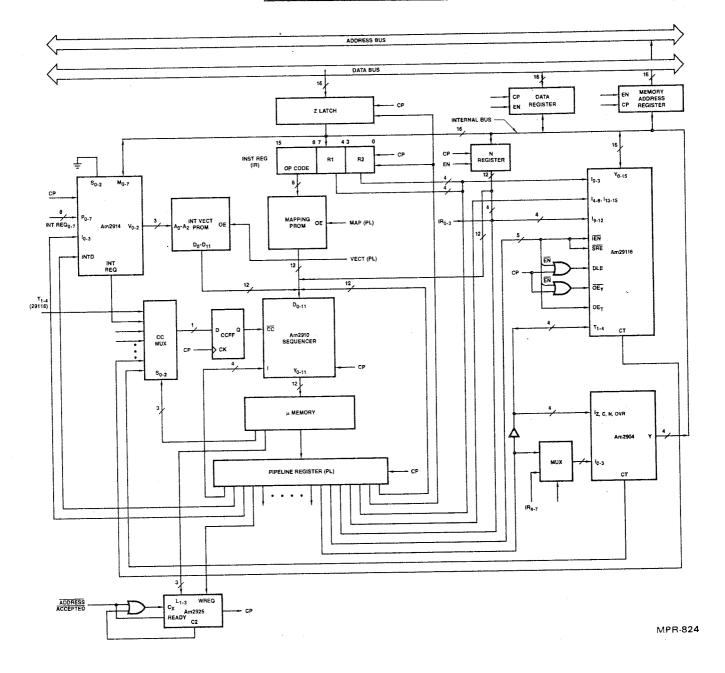

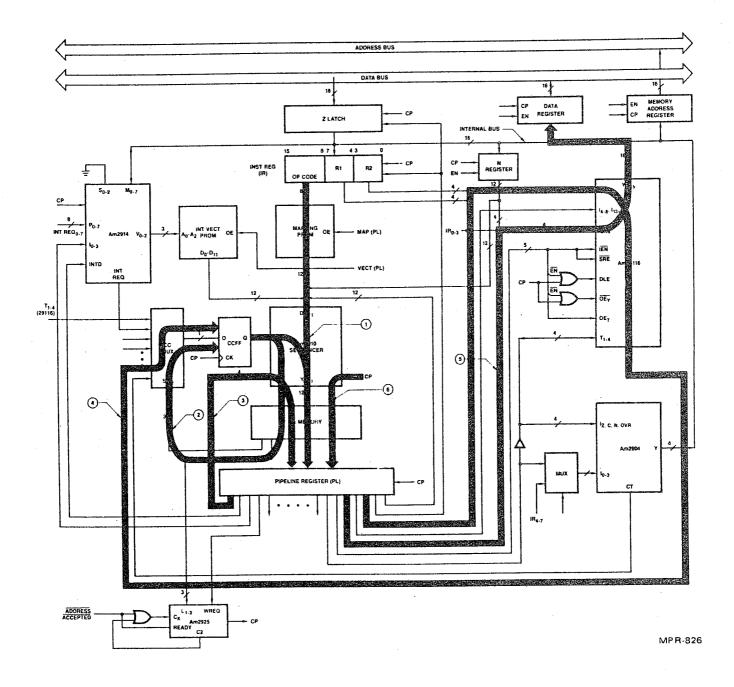

# Central Processing Unit Block Diagram

# A Microprogrammed CPU Using Am29116 (continued)

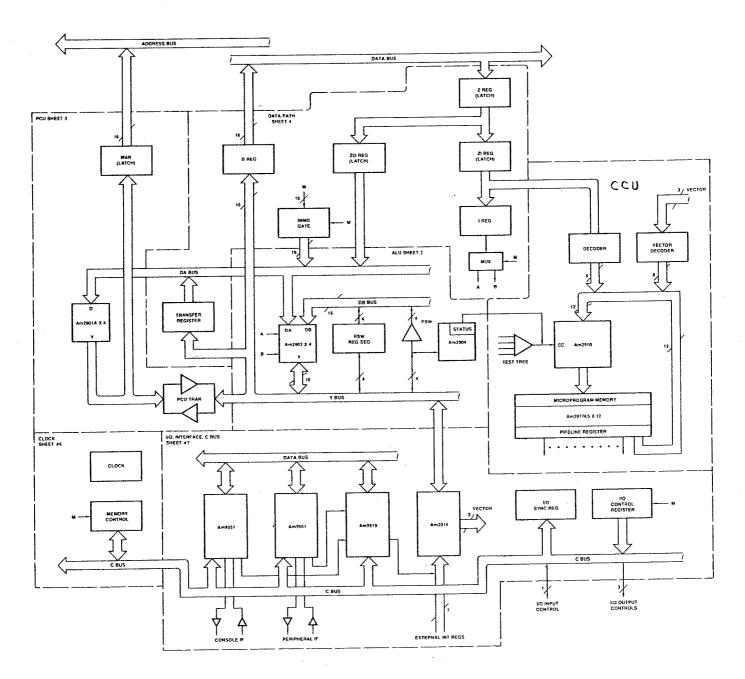

### System Organization

This is a simple system comprised of:

- 16-bits wide main memory built from static RAM chips

- Am29116 processor and CCU

- A simple bus structure:

- can be modified to accomodate interface signals

- but to add other  $I/\emptyset$  devices, a bus controller is needed

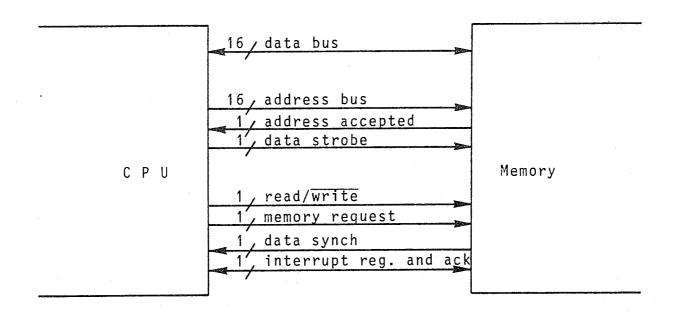

# System Organization (continued) Interface Signals between the Memory and the CPU

- · handshaking over three busses

- 16-bit-wide address bus

- 16-bit-wide bidirectional data bus

- 7-bit-wide control bus

- · memory request

- · read/write

- · address accepted

- · data strobe

- · data synch

- · interrupt control lines

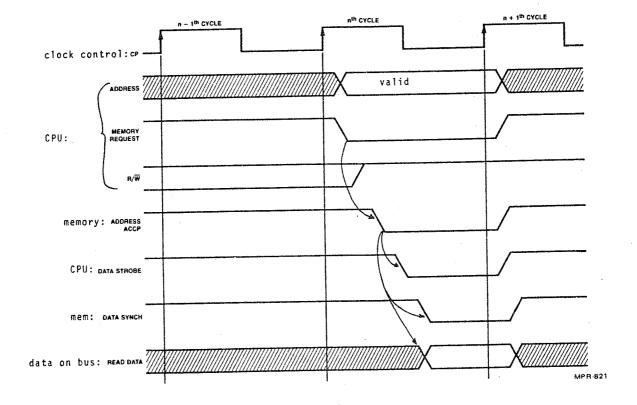

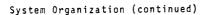

# Memory Read (continued)

- To use the data in the n+1<sup>th</sup> cycle, the Am29116 generates the main memory address during the (n-1)<sup>th</sup> cycle.

- Data is read during the n<sup>th</sup> cycle.

- The n<sup>th</sup> cycle must be stretched to accomodate main-memory READ timing.

- The signal to stretch the n<sup>th</sup> cycle is provided to the Am2925 clock generator during the (n-1)<sup>th</sup> cycle.

#### Instruction Formats

(same as for Super-16)

• One-word instructions (16 bits):