Volume I Q20000 Series

# Bipolar Logic Arrays

Applied MicroCircuits Corporation

# (210)

The material in this document supersedes all previous documentation issued for any of the products included herein.

AMCC reserves the right to make changes to any product herein to improve the reliability, function or design.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC performs quality conformance inspection as defined by the customers' source control drawing.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC, MacroMatrix, RaceCheck, and Sea-of-Cells are registered trademarks of Applied Micro Circuits Corporation.

AMCC holds the patents for the Clock Driver Output, U.S. Patent 4,970,414. Japan Patent 2.177686.

AMCC holds the patents for the Turbo design: U.S. Patent 4,835,420; U.S. Patent 4,874,970; U.S. Patent 4,926,065.

AMCC recognizes the following trademarks throughout this design manual:

- Cadence Cadence Design Systems, Inc.

- DAZIX Daisy / An Intergraph Company

- LASAR Version 6 Teradyne, Inc.

- Mentor Mentor Graphics Corporation

- Sun Sun Microsystems Corporation

- Valid Cadence Design Systems, Inc.

- Verilog Cadence Design Systems, Inc.

- Synopsys Synopsys, Inc.

Copyright 1992 Applied Micro Circuits Corporation PRINTED IN U.S.A.

November 15, 1992

#### Dear AMCC Customer:

We are pleased to provide you with an enhanced edition of our MacroMatrix design software. MacroMatrix has undergone several significant modifications to improve ease-of-use and design correctness that require your careful attention. Several new tools have been added for placement, packaging support, and design submission automation. Please refer to the accompanying MacroMatrix Newsletter for details.

MacroMatrix News also contains updated information regarding third party design tool support and steps needed to install and transition your design to this new release. Conversion of your existing MacroMatrix installation to this new installation should take no more than 1 hour. All designs submitted to AMCC after January 1, 1993, will have to use this new software for design verification (except Mentor 7.X users). No exceptions will be permitted. Customers planning to submit designs prior to that date have the option of continuing to use the previous software.

Included with this shipment are the new Volume 2 and Volume 3 of the AMCC MacroMatrix design manuals. These manuals supersede all previous versions of Volume 2 of the MacroMatrix Design Manual.

Should you have any questions regarding the appropriate usage of this new software release, please do not hesitate to contact any of our application engineers, sales representatives, or your assigned AMCC implementation engineer.

Sincerely,

Jeff Hilbert

ASIC Business Unit Director

# $\mathbf{From} \ \mathbf{AMCC} \dots$

# MacroMatrix News

October 1992

#### INTRODUCING RACECHECK

RaceCheck is a tool developed by AMCC for verifying that no problems exist in the test vectors to be used for automated test. RaceCheck incorporates Teradyne's LASAR 6<sup>TM</sup> simulator into an easily executable form. A series of translators for getting data from AMCC generic format into LASAR format and back to AMCC generic format have been provided.

The entire process, including running LASAR and checking the results, has been encased into a shell that prompts the user for needed information and then submits the process to a job queue for actual execution.

#### WHY USE RACECHECK

Prior to the use of this type of tool, AMCC's experience showed that a number of designs required the presence of an AMCC implementation engineer at test in order to debug the test itself. This could impact delivery schedules. The use of this kind of tool by AMCC has virtually eliminated the need for debugging test patterns on the tester. The vector races can now be debugged on a simulator early in the design cycle where the process is much simpler and much faster.

Delays may be incurred due to the time it takes to send information back and forth between AMCC and our customers. Customer assistance is sometimes needed to help debug a problem, and customer approval is always required to make design or test vector changes. The placing of RaceCheck in the hands of our customers will reduce the time required to process an NRE after submission to AMCC and therefore improve the delivery schedule.

#### AMCCPACKAGE

The amccpackage software package provides direct on-line access to the AMCC Package Data Base on all AMCC-supported engineering work-stations and platforms. AMCC customers will now be able to interrogate the list of available packages by array type and technology at any point in the design process, and generate output files containing the pad to pin connections, power plane availability and pin capacitance information with or without a design netlist being present.

Once the design has reached the stage where a netlist has been created, amccpackage is used to check that the captured design will fit in the package selected. If the design does fit, then the amccpackage program will generate the output.dly file for use by the amccann annotation software program.

#### AMCCSUBMIT

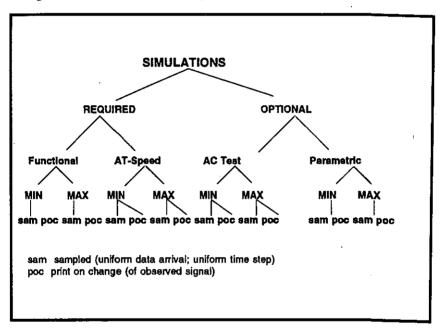

The amccsubmit software package is a new program that is run by the customer when their design is ready for submission to AMCC for processing; that is, after the design has been captured, simulated, and reviewed to the designer's satisfaction. amccsubmit simplifies the design submission process via its easy-to-use menu-driven style of data entry. amccsubmit is used by AMCC customers to describe all of the simulations and tests that must be performed to verify the "goodness" of the circuit design, whether the simulations involve functional tests, AC tests, parametric tests, or at-speed simulations. The design validation and customer description information also may be entered on the customer's work-station via this software package.

amccsubmit generates a clear and concise design submission report, simplifying the documentation and hand-off processes for both AMCC and our customers. amccsubmit is a major step forward in the pursuit of a paper-less and error free design submission process.

#### **MENTOR 8.1**

MacroMatrix software running under Release 8.0 from Mentor Graphics is under development for AMCC customers. There is a Mentor software bug which has delayed our conversion to Mentor 8.0. We are currently working with Mentor to resolve the issue and plan to release MacroMatrix on Mentor 8.1 late in 1992.

### Synopsys Support

AMCC has added Synopsys synthesis support for the Q20000 Series of ECL/TTL Logic Array family. We have added a technology library for the Q20000 series for the Design Compiler tool from Synopsys, which is normally used for CMOS and BiCMOS designs. You do not need to purchase the separate ECL Design Compiler tool in order to apply logic synthesis techniques to your Q20000 array design! A set of "release notes" is available that describes in detail AMCC's support for Synopsys tools. The Q20000 library support adds to our previous support of Design Compiler for our Q24000 BiCMOS arrays.

# PLL Arrays - CRU and CSU Macro and 8B/10B Functional Block Distribution

Not included in the normal library release tapes are the specialized macro functions for AMCC's Q20P010 and Q20P025 PLL arrays. Please contact AMCC for additional information on usage and distribution of CRU and CSU macros and other functional blocks, including certain non-disclosure requirements as applicable.

### Changes to the Q20000 Library

The index to Section 6 - Macro Library Documentation - identifies changes made to individual macros. Some Tpd timing delays have been respecified. PW, fmax, k-Factors are respecified for some macros and they are identified in the index. A few new macros have been added.

For PLL macros, they are now documented as individual macros. However, they are not included in the release tape. Contact AMCC if you wish to use PLL macros.

# TABLE OF CONTENTS

# TABLE OF CONTENTS

# SECTION 1 INTRODUCTION

| Introduction to Volume I                | 1.3  |

|-----------------------------------------|------|

| Summary of Volume I                     | 1.4  |

| Summary of Volume II                    | 1_4  |

| Summary of Volume III                   | 1-5  |

| Workstation and System Operation        | 1-5  |

| EWS-Specific Rules                      | 1-5  |

| Installation of the Library And Patches | 1-5  |

| Design Validation Document              | 1-5  |

| Design Submission Document              | 1-6  |

| MacroMatrix User's Guides               | 1-6  |

| Glossary, Index                         | 1-6  |

| Trademarks                              | 1-6  |

| Design Support Interface                | 1-7  |

| Schematic Entry                         | 1-7  |

| amccerc                                 | 1-8  |

| amccpackage                             | 1-9  |

| amccann                                 |      |

| Simulations                             | 1-10 |

| amecsimfmt                              | 1-12 |

| racecheck                               | 1-12 |

| amccure                                 | 1-12 |

| amecsubmit                              | 1-12 |

| Design Approval                         | 1-15 |

| Back-Annotation                         | 1-15 |

| Simulators                              | 1.15 |

| &20000 Series Description               | 1-16 |

| Equivalent Gates - Relative Sizing      | 1-17 |

| Circuit Density                         | 1-17 |

| Macro Library                           | 1-18 |

| 1 ypical Applications                   | 1-18 |

| Features                                | 1_19 |

# SECTION 2 DESIGN METHODOLOGY

| Design Methodology                              | 2-3   |

|-------------------------------------------------|-------|

| Technology                                      |       |

| Array Architecture                              | 2.3   |

| PLL Array Description                           | 2-5   |

| Digital Logic                                   | 2-5   |

| Phase-Locked Loop Macros                        | 2-5   |

| Encoding/Decoding                               | 2-7   |

| Flexible I/O Structure                          | 2-7   |

| Array Cell Resources                            | 2-7   |

| Turbo Driver                                    | 2-7   |

| Thermal Diode, AC Speed Monitor                 | 2.9   |

| Macro Configuration                             | 2-10  |

| Interconnections and Routing                    | 2-10  |

| Logic Cells                                     | 2-11  |

| I/O Cells                                       | 2-11  |

| Overhead Circuitry                              | 2-11  |

| Macro PAD Names - Changes                       | 2-11  |

| Interface Options                               | .2-12 |

| Interface Guidelines                            | 9-19  |

| Interface Macro Guidelines, DECL                | 2-13  |

| Interface Macro Guidelines, ECL - single supply | .2-14 |

| Interface Macro Guidelines - ECL/TTL mixed      |       |

| mode                                            | .2-15 |

| Interface Macro Guidelines - ECL/TTL single     |       |

| supply                                          | .2-16 |

| Macro Summary                                   | .2-17 |

| I/O Macros                                      | .2-17 |

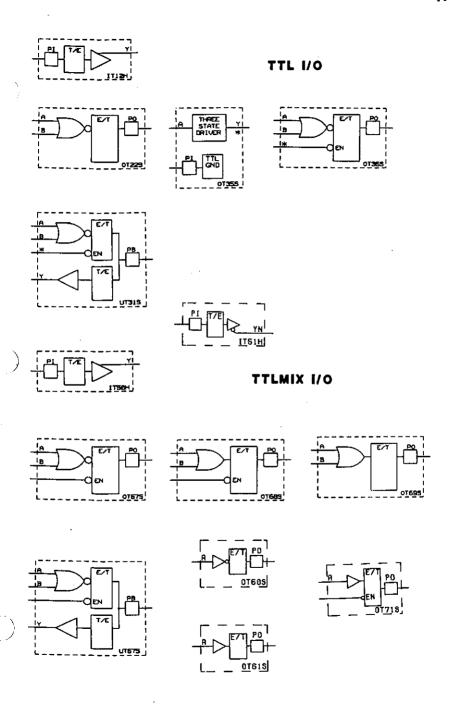

| TTL Input (ITxx macros)                         | 2-18  |

| TTL Output (OTxx macros)                        | 2-18  |

| Bidirectional TTL (UTxx macros)                 | 2-18  |

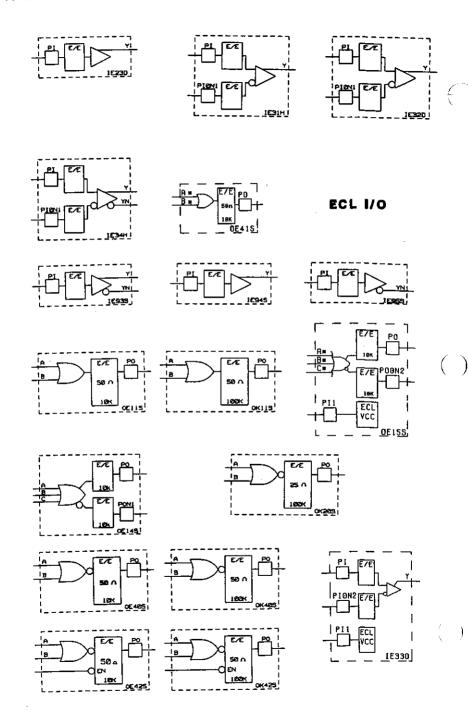

| ECL Input (IExx macros)                         | 2-19  |

| ECL Output (OExx, OKxx macros)                  | 2-19  |

| Darlington ECL outputs                          | 2-20  |

| CML Outputs (Open Collector)                    | 2-20  |

| On-Chip Series Terminated Outputs               | 2-20  |

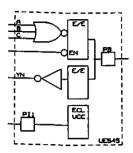

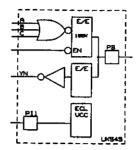

| Bidirectional ECL (UExx, UKxx macros)           | 2-21  |

| +2-5V Reference ECL/TTL                         | 2-21  |

| Alternative ECL Terminations                    | 2-21  |

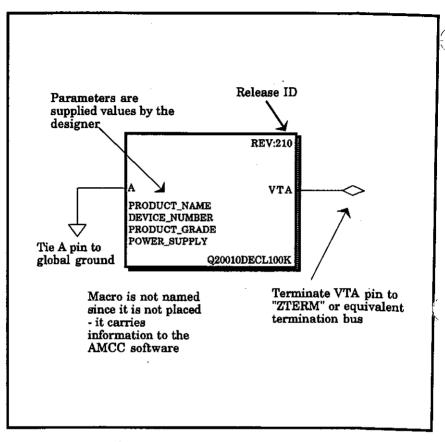

| Characterizing the Array - The Chip Macros      | 2-22  |

| AMCCERC Technology Check                        | 2-22  |

| Fixed Power and Ground Placement                | 2-22  |

| AC Speed Monitor Fixed Pads                     | 2-25  |

| Thermal Diode Fixed Pads                        | າ ຄຣີ |

| Power Busses and Added Power and Ground2-20                       | œ        |

|-------------------------------------------------------------------|----------|

| Adding Extra Power and Ground - IEVCC22                           | 7        |

| Additional IEVCC22                                                | 7        |

| Adding Extra Power and Ground - ITPWR, ITGND2-28                  | j        |

| Additional ITPWR, ITGND22                                         | 0        |

| Specific Additional Description and County                        | 2        |

| Specifying Additional Power and Ground                            | <i>j</i> |

| Cell Efficient Macros22                                           |          |

| SWGROUP Parameter/Property2-22                                    | •        |

| Added Power and Ground Placement2-2                               | •        |

| Macro Pin Fan-in Loading                                          | J        |

| Internal Fan-out.                                                 | )        |

| Derating Fan-Out Limits                                           | J        |

| Static Signals                                                    | Ţ        |

| Internal Cell Utilization2-33                                     | 2        |

| Internal Pin Count Limit2-33                                      | 2        |

| 090000 G-1 P 1 P 1 P 1 P 1 P 1 P 1 P 1 P 1 P 1 P                  |          |

| Q20000 Series Basic Design Rules and Guidelines 2-3               | ŧ        |

| Power Bus Distribution and Decoupling2-38                         | 5        |

| Phase-Locked Loop 2-40                                            |          |

| Special Engineer                                                  | J        |

| Special Features                                                  | )        |

| Bit Error Rate Test (BERT)                                        | 2        |

| Loopback Mode246                                                  | 2        |

| Local Loopback                                                    | ) .      |

| Link Loopback                                                     | 2        |

| Test/Bypass Mode24                                                |          |

| Lock Detect                                                       | j        |

| Frequency Synthesis Macros                                        |          |

| Specifications                                                    |          |

| Input Reference Frequency2-49                                     |          |

| Reference Clock Jitter2-49                                        |          |

| Input Reference Stability249                                      | )        |

| Acquisition Time2-4                                               |          |

| Edge jitter2-4                                                    | •        |

| Supply Voltage Sensitivity2-49                                    | }        |

| Clock Recovery Macros                                             | )        |

| Test Vectors for PLL-based ASSP's2-50                             | )        |

| The Q20M100 Memory Array (TBS)2-5                                 | 1        |

| A 11 1                                                            |          |

| Appendix 2-A                                                      | _        |

| Distributed Capacitive Load and High Frequency Loading Effects2-A | 1        |

| Transmission Line Discontinuities2-A                              | <u>1</u> |

| Distributed Loading2-A                                            | -2       |

| Lumped Loading2-A                                                 | 3        |

## SECTION 3 TIMING ANALYSIS

| Cimi | ng Analysis                                  | 3-3   |

|------|----------------------------------------------|-------|

|      | Computing Propagation Delay                  | 3-3   |

|      | Preliminary Computation - Prior to Capture   | 3-3   |

|      | Front-Annotation - After Capture             | .3-4  |

|      | Back-Annotation - After Layout               | .3-4  |

|      | Individual Macro Propagation Delays          | .3-4  |

|      | Intrinsic Set-Up and Hold Times              | 3-6   |

|      | Recovery Time                                |       |

|      | Pulse Width                                  | .3-6  |

| •    | Maximum Operating Frequency                  | 3-7   |

|      | Computing Loading Delay - Output Net         | .3-9  |

|      | Computing Loading Delay - Internal Net       | .3-11 |

|      | Computing Lnet                               | .3-11 |

|      | Computing Lfo                                | .3-11 |

|      | Front-Annotation Table for the PLL Arrays    | .3-13 |

|      | Front-Annotation Estimated Metal Loads       | .3-13 |

|      | Result                                       | .3-14 |

|      | Result                                       | .3-14 |

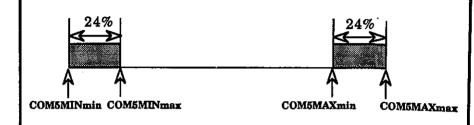

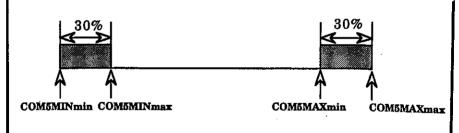

|      | Computing COM5MINmax from COM5MINmin, etc    | .3-14 |

|      | The Adjustment Factors                       | .3-14 |

|      | Converting COM5 to COM4                      | .3-14 |

|      | Converting MIL5 to MIL4                      | .3-14 |

|      | Using the Libraries                          |       |

|      | Example                                      |       |

|      | Design Submission Extremes                   | .3-16 |

|      | AMCCANN File Names                           | .3-17 |

|      | Asymmetry in the Worst-Case Path             | .3-18 |

|      | Internal Signal Tracking Guideline           | .3-18 |

|      | Signal Balancing                             | .3-21 |

|      | Distortion Minimization                      | .3-21 |

|      | Front-Annotation Load Units                  | .3-22 |

|      | Estimated Front-Annotation Load Units        | .3-22 |

|      | Back-Annotation Load Unit Conversion Factors | .3-23 |

|      | Back-Annotation Conversion Factors           | .3-23 |

|      |                                              |       |

# SECTION 4 EXTERNAL SET-UP AND HOLD TIMES

| External Set-Up and Hold Times        | 4-3 |

|---------------------------------------|-----|

| Introduction                          | 4-3 |

| Set-Up Time - Generic Equation        | 44  |

| tauexternal                           | 44  |

| tsuCOM5MAX                            |     |

| tsuMIL5MAX                            | 44  |

| tsuMIL5MIN                            | 44  |

| tauCOM5MIN                            | 44  |

| Hold Time - Generic Equation          | 45  |

| thMIL5MAX                             | 4-5 |

| thMIL5MIN                             | 4-5 |

| thCOM5MAX                             | 4-5 |

| thCOM5MIN                             | 45  |

| Converting COM5 to COM4, MIL5 to MIL4 |     |

| Set-Up Times                          | 4-8 |

| tsuCOM4MAX                            | 4-8 |

| tsuMIL4MAX                            |     |

| tsuMIL4MIN                            | 4-8 |

| tsuCOM4MIN                            | 4-8 |

| Hold Times                            |     |

| thMIL4MAX                             |     |

| thMIL4MIN                             |     |

| thCOM4MAX                             |     |

| thCOM4MIN                             | 4-9 |

# SECTION 5 POWER COMPUTATIONS

| Power Computation 5-3                                  |

|--------------------------------------------------------|

| Macro Options                                          |

| State-Dependent Current                                |

| PART 1                                                 |

| Macro DC Power Dissipation5-4                          |

| Computing The Maximum Worst Case DC Power- Summary 5.4 |

| Macro Occurrence Table                                 |

| Worst-Case Maximum Current Multiplication Factors 5 5  |

| Compute the Total Typical Interface Macro Current 5 &  |

| Compute the Worst-Case Interface Current 5 c           |

| Compute the Total Typical Internal Macro Current 5 &   |

| Compute the Worst-Case Internal Current 5 &            |

| Compute the Total Typical Overhead Current             |

| Compute The Worst-Case Overhead Current 57             |

| Sum The ICC and IEE Currents                           |

| Multiply by the Worst-Case Voltage                     |

| ECL Static Power Peo                                   |

| ECL Output Termination Current                         |

| When 50 OHM or 25 OHM Terminations Not Used5-9         |

| When VT ≠ -2V                                          |

| ECL Termination Current - Darlington ECL Output5-10    |

| ECL Termination Current                                |

| CML Macros                                             |

| Sum the Result - Total DC Power                        |

| Macro Occurrence                                       |

| DC Power Dissipation AMCCERC Report                    |

| Adjusting the Computed DC Power Result5-11             |

| 0-11                                                   |

| PART 2                                                 |

| AC Power Dissipation5-7                                |

| Macro Occurrence Worksheet                             |

| Computing an Estimate of AC Power Dissipation 5.9      |

| ECL Darlington output macros 5.9                       |

| ECL inputs                                             |

| internal macros5-8                                     |

| PART 3                                                 |

| Final Regult                                           |

# SECTION 6 MACRO LIBRARY DOCUMENTATION

# **Macro Documentation**

See index in Chapter 6

# SECTION 7 PLACEMENT

| Introduction to Placement                 | 7-3 |

|-------------------------------------------|-----|

| High-Frequency Guidelines                 | 7-3 |

| Placement - High-Frequency Pins           | 7-3 |

| Differential Interface - When Recommended | 7-3 |

| Isolation with Ground                     | 7-3 |

| PLL Arrays - Placement of PLL Macro       | 7-4 |

| Added Power and Ground Macros             | 7-4 |

| Dual I/O Cell Macros                      | 7-4 |

| Die Plots                                 |     |

# SECTION 8 PACKAGE SELECTION

| Package Selection                                     | 8-3  |

|-------------------------------------------------------|------|

| Introduction                                          | 8-3  |

| Required to Start                                     | 8-3  |

| AMCCERC.LST Population Report - Required Package Pins | 8-3  |

| Minimum Package Signals Pins Required                 | 8-3  |

| Maximum Required Package Signal Pins                  | 8-4  |

| Actual Required Package Signal Pins                   | 8-4  |

| Package Selection and AMCCANN                         | 8-6  |

| Computing the Junction Temperature                    | 8-7  |

| Computing Junction Temperature - Commercial           | 8-7  |

| Computing Junction Temperature - Military             | 8-8  |

| Placement - See Section 7                             | 8-9  |

| Standard Packages                                     | 8-9  |

| PLL Array Packages                                    | 8-10 |

| SECTION 3 OF EMATEM COMMITTONS                           |      |

|----------------------------------------------------------|------|

| Otion Conditions                                         |      |

| Operating Conditions                                     | 9-3  |

| Introduction                                             | 9-3  |

| Commercial Specification                                 | 9-3  |

| Circuit with a -4.5V supply                              | 9-3  |

| All other circuits                                       | 9-3  |

| Military Specification                                   | 9-3  |

| Circuit with a -4.5V supply                              | 9-3  |

| All other circuits                                       | 9-3  |

| Minimum Propagation Delay                                | 94   |

| Library Specifications                                   | 9-4  |

|                                                          |      |

| Appendix - Operating Condition Table from the Data Sheet |      |

|                                                          |      |

|                                                          |      |

| SECTION 10 TESTING - INTRODUCTION                        |      |

| 1 11 11 11 11                                            |      |

| Introduction to Testing                                  | 10.9 |

| Circuit Testability                                      | 10.0 |

| Structured Design for Test [DFT]                         | 10.0 |

| Circuit Testability Applysis                             | 10-3 |

| Circuit Testability Analysis                             | 10-3 |

| Circuit Simulation Requirements                          | 10-4 |

| Functional Simulation - Required                         | 10-5 |

| Guidelines                                               | 10-5 |

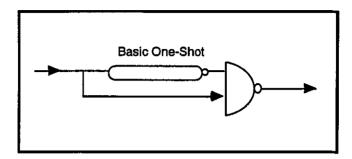

| Hazards, Races                                           | 10-6 |

| атсечте                                                  |      |

| Fault-Grading                                            | 10-7 |

| At-Speed Simulation - Required                           | 10-7 |

| AC Speed Monitor                                         | 10-8 |

| AC Tests Simulation - Optional                           | 10-8 |

| amccvrc and amccsubmit                                   | 10-8 |

| Parametric Testing - Optional - may be Required          | 10-9 |

| amccvrc                                                  | 10-9 |

| amccsubmit                                               | 10.9 |

SECTION O ODEDATING COMPUTANCE

## SECTION 11 QUICKSHEETS

## SECTION 12 INDEX

# **TABLES**

| Table 1-1   |                                                                   |                |

|-------------|-------------------------------------------------------------------|----------------|

| Table 1-1   | Supported Arrays                                                  | 1-4            |

| Table 1-2   | Sizes of the AMCC Bipolar Arrays                                  | 1-18           |

|             | •                                                                 |                |

| Table 2-1   | I/O and Internal Cell Resources                                   | 2-8            |

| Table 2-2   | Fixed PAD Numbers for                                             | 2.0            |

| Table 2-3   | Power and Ground PAD Resources.                                   | 20             |

| Table 2-4   | Power Supply Options                                              | Z-9            |

| Table 2-5   | I/O Mosto Dominant-tim I-Ja-                                      | 2-12           |

| Table 2-6   | I/O Macro Documentation Index                                     | 2-17           |

| Table 2-7   | ECL Macro Selection Matrix                                        | 2-19           |

| Table 2-7   | Chip Macros and I/O Modes.                                        | 2-2:           |

|             | Additional IEVCC, Additional TTL Power and Ground                 | 2-27           |

| Table 2-9   | Derating Guideline                                                | 2-30           |

| Table 2-10  | Maximum Internal Pin Count Limits                                 | 2-33           |

| Table 2-11  | Fan-Out Derating                                                  | 2-34           |

|             | •                                                                 |                |

| Table 3-1   | Macro Specifications Provided                                     | 3-4            |

| Table 3-2   | Maximum Operating Frequency and Pulse Width                       |                |

| Table 3-3   | Example k-Factors - COM5MAX library                               | 2.10           |

| Table 3-4   | continued                                                         | 9 19           |

| Table 3-4   | Front-Annotation Estimated Metal Loads                            | 0.10           |

| Table 3-5a  | Timing Adington of England House                                  |                |

| - abic b-ba | Timing Adjustment Factors                                         | 3-10           |

| Table 3-5b  | [MAXmin to MAXmax and MINmax to MINmin]                           | 3-15           |

| rante 9-90  | Timing Adjustment Factors                                         | 3-15           |

| M-1.1 o o   | [COM5 to COM4 and MIL5 to MIL4]                                   | 3-15           |

| Table 3-6   | Library Selection                                                 | 3-16           |

| Table 3-7   | AMCCANN Delay File Names                                          | 3-17           |

| Table 3-8   | Estimated Front-Annotation Load Units                             | 3-22           |

| Table 3-9   | Back-Annotation Load Units Conversion Factors                     | 3-23           |

|             |                                                                   |                |

| Table 4-1   | Set-Up Time Equations [COM5, MIL5]                                | 4.4            |

| Table 4-2   | Hold Time Equations [COM5, MIL5]                                  | 4.5            |

| Table 4-3   | Terminology Definitations                                         | 4.6            |

| Table 4-4   | Set-Up Time Equations [COM4, MIL4]                                | 4-0            |

| Table 4-5   | Hold Time Pourties (COM4, MILIA)                                  | 4-0            |

| Tuble To    | Hold Time Equations [COM4, MIL4]                                  | 4-9            |

| l'able 5-1  | W                                                                 |                |

| Table 5-1   | Worst-Case Current Multipliers                                    | 5-5            |

|             | Typical Overhead Current in mA                                    | 5-7            |

| Table 5-3   | Worst-Case Voltages                                               | 5-8            |

| rable 5-4   | ECL 10K/100K Termination Current                                  | 5-9.           |

|             |                                                                   | -              |

| Table 8-1   | Array Pad Count Limit                                             | 8-4            |

| Table 8-2   | Standard Packaging Matrix                                         | 8.5            |

| lable 8-3   | AMCCANN Default Package Pin Capacitance                           | 9.8            |

| Table 8-4   | Packaging Matrix - Ojc                                            | 8.0            |

|             | - warmania and the - Ojuminianianianianianianianianianianianiania | 0-5            |

| able 9-1    | Magra Libraries                                                   | 0.4            |

|             | Macro Libraries                                                   | <del>У-4</del> |

# **FIGURES**

| Figure 1-1a | Creating the Netlist1-7                                                        |

|-------------|--------------------------------------------------------------------------------|

| Figure 1-1b | agif through amccann                                                           |

| Figure 1.1c | Simulations (several are Required)1-11                                         |

| Figure 1.1d | From Simulation Output Reformat to amccsubmit1-13                              |

| Figure 1.1e | Design Submission Through Prototype Approval1-14                               |

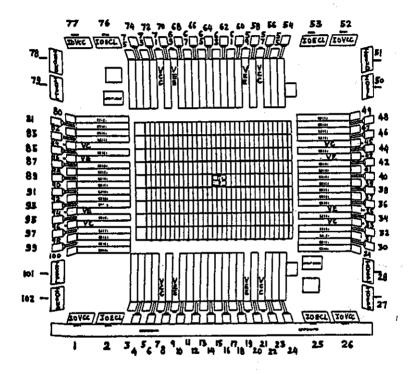

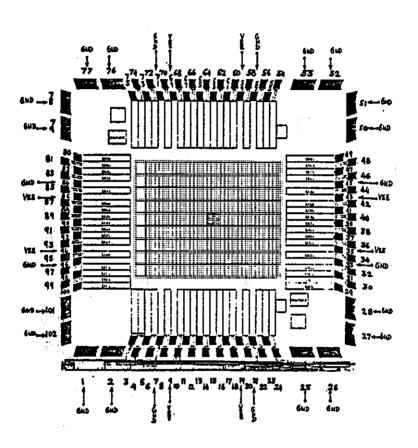

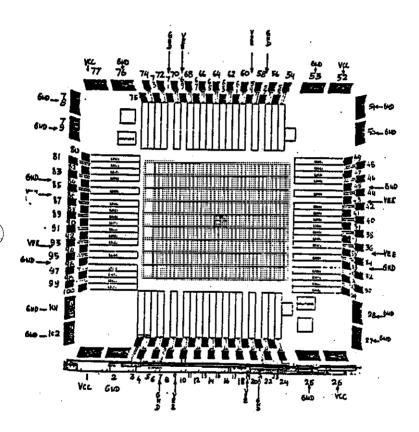

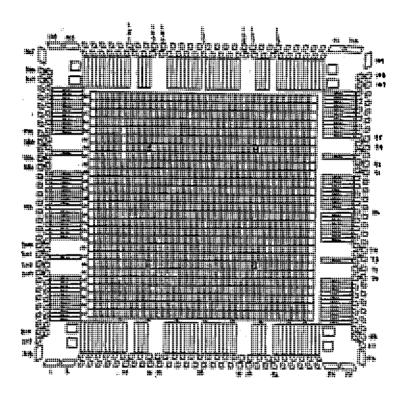

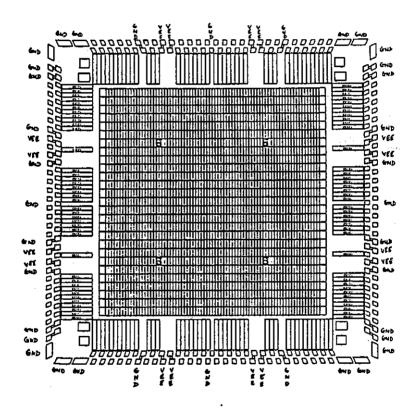

| Figure 2-1  | Q20080 Die Plot24                                                              |

| Figure 2-2  | Phasa-I asked I con                                                            |

| Figure 2-3a | Phase-Locked Loop                                                              |

| Figure 2-3a | 100% ECL Interface - Dual Supply (DECL)213                                     |

|             | 100% ECL Interface 2-14 Mixed ECL/TTL Interface - Dual Supplies 2-15           |

| Figure 2-3c | Mixed ECL/TTL interface - Dual Supplies2-15                                    |

| Figure 2-3d | Mixed ECL/TTL Interface                                                        |

| Figure 2-4  | Sample Chip Macro                                                              |

| Figure 2-5  | AC Speed Monitor                                                               |

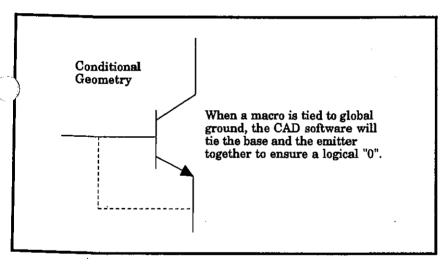

| Figure 2-6  | Effective Global Ground                                                        |

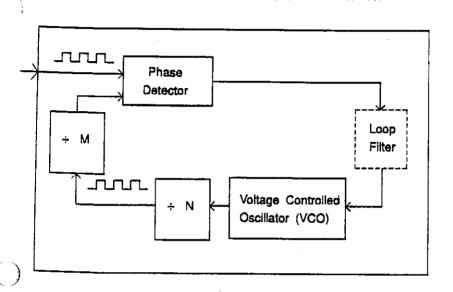

| Figure 2-7  | Phase-Locked Loop Block Diagram241                                             |

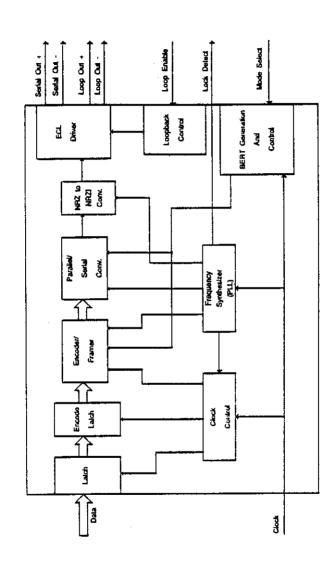

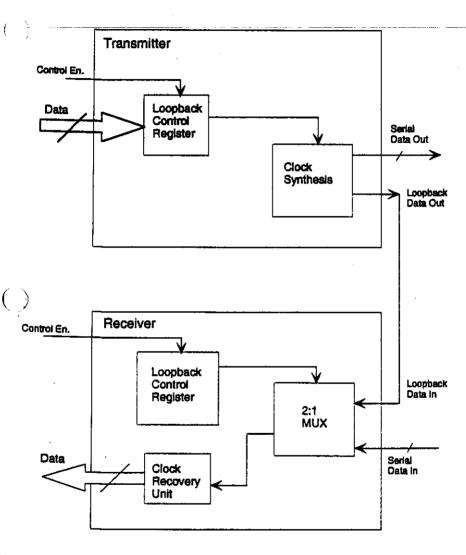

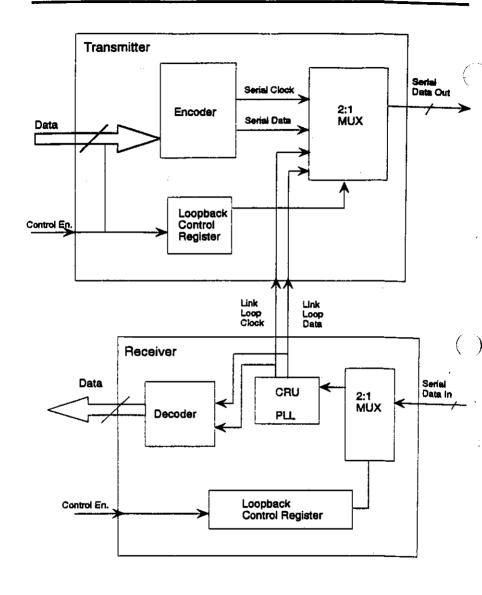

| Figure 2-8  | Representative Transmitter Block Diagram242                                    |

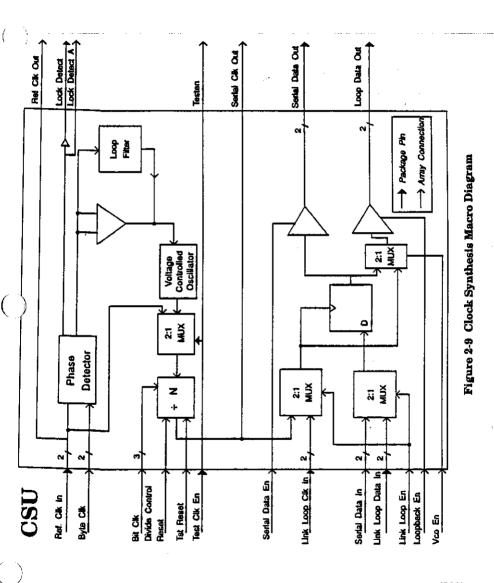

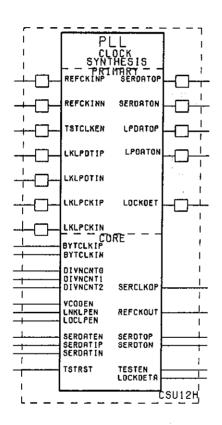

| Figure 2-9  | Clock Synthesis Macro Diagram243                                               |

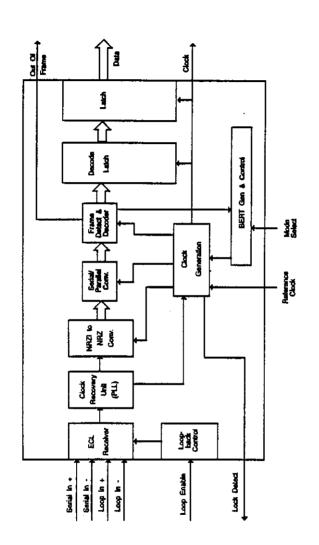

| Figure 2-10 | Representative Receiver Block Diagram 2-44                                     |

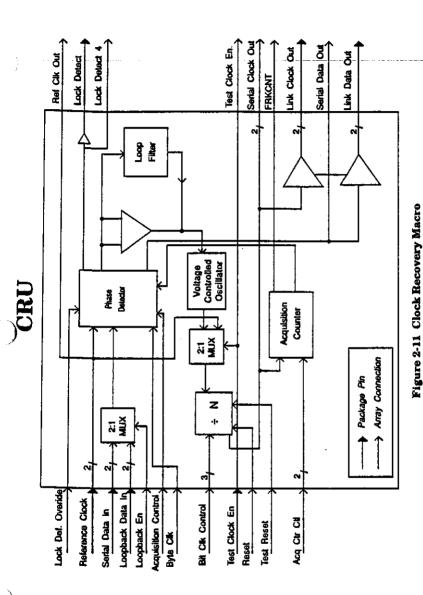

| Figure 2-11 | Clock Recovery Macro Diagram 2-45                                              |

| Figure 2-12 | Local Loopback Block Diagram 2-47                                              |

| Figure 2-13 | Link Loopback Block Diagram                                                    |

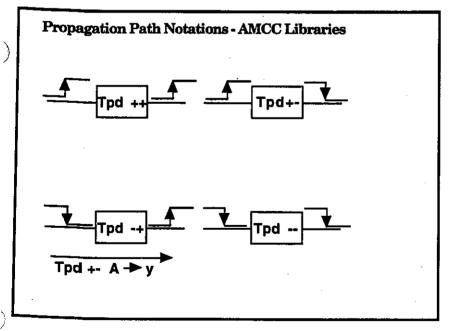

| Figure 3-1  | Tpd Specifications [conventions]3-5                                            |

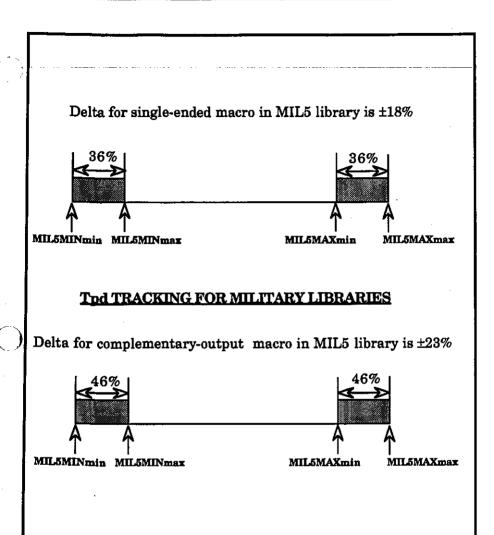

| Figure 3-2a | Example of Tracking for the MIL5 Operating                                     |

| B           | Conditions 2 to                                                                |

| Figure 3-2b | Conditions                                                                     |

| B           |                                                                                |

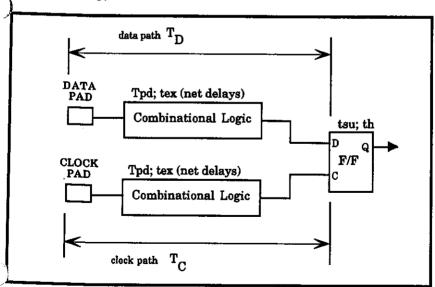

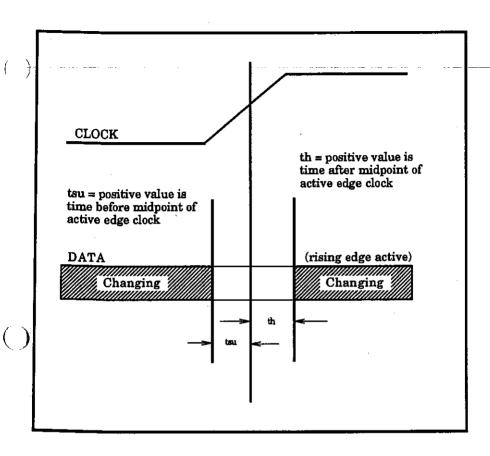

| Figure 4-1  | External Set-Up and Hold Times4-3                                              |

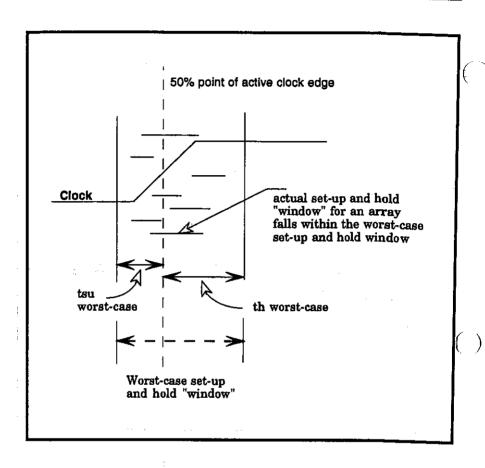

| Figure 4-2  | External Set-Up and Hold Times - Interpretation 4-10                           |

| Figure 4-3  | Worst-Case Range4-11                                                           |

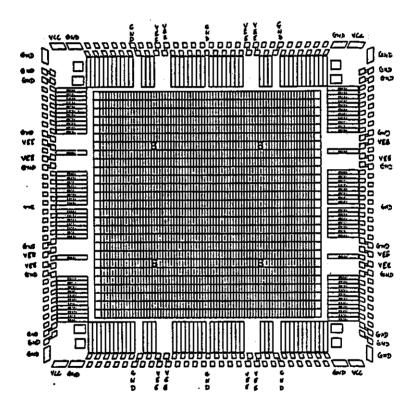

| Figure 7-1  | Q20010 Floor Plan                                                              |

| Figure 7-2  | Q20010 Power Pad Designation - 100% ECL                                        |

| Figure 7-3  | Q20010 Power Pad Designation - Mixed TTL, ECL Mode7-7                          |

| Figure 7-4  | Q20080 Chin Floor Plan                                                         |

| Figure 7-5  | Q20080 Chip Floor Plan 7-8<br>Q20080 Power Pad Designation - 100% ECL Mode 7-9 |

| Figure 7-6  | Q20080 Power Pad Designation - Mixed TTL, ECL Mode7-10                         |

| Figure 9-1  | Commercial libraries for COM5 circuits9-3                                      |

| Figure 10-1 | Circuit Simulation Requirements10-4                                            |

| Figure 10-2 | A basic One-Shot Circuit                                                       |

|             |                                                                                |

# SECTION 1 INTRODUCTION

# Introduction to Volume I

This design manual provides a summary of the AMCC (Applied Micro Circuits Corporation) Q20000 Turbo Series Logic Arrays. Volume I is composed of the following sections:

Section 1: Introduction

Section 2: Design Methodology and Design Rules

Section 3: Timing Analysis; Path Delay

Section 4: External Set-Up and Hold Time Analysis

Section 5: Power Computation/Placement/Packaging

Section 6: Macro Library Documentation

Section 6-1: TTL Interface Section 6-2: TTLMIX Interface Section 6-3: ECL Interface

Section 6-4: Internal Logic Macros Section 6-5: Chip Macros; VBB Macros;

Added Power and Grounds; PLL Macros

Section 7: Placement Rules

Section 8: Packaging; Junction Temperature

Section 9: Operating Conditions Section 10: Testing Requirements Section 11: Macro Quicksheets

Section 12: Index

## It also includes information on:

Product features

• Performance specifications

Design Interface and support

List of available macros

The AMCC Packaging Brochure should also be referenced for further information on packaging.

The Q20000 Series supports the arrays shown in Table 1-1.

|            | LE 1-1.<br>ED ARRAYS |

|------------|----------------------|

| Q20120     |                      |

| Q20M100 ** |                      |

| Q20080     |                      |

| Q20045     | PLL:                 |

| Q20025     | Q20P025              |

| Q20010     | Q20P010              |

| Q20004**   |                      |

| <u> </u>   | Q20P001**            |

#### \*\* Advance Information

#### SUMMARY OF VOLUME I

Volume I of this three-volume design manual is intended as a self-contained design aid to allow the proper selection of an array for a particular design, to indicate the packaging available for that array, and to provide the designer with a better understanding of the capabilities of the Q20000 Turbo Series Bipolar Logic Arrays.

Section 2 contains design rules specific to this array series.

The macro summary and detailed macro specifications are presented in reference manual format in Section 6 with a rapid graphic reference provided by Quicksheets in Section 11. Either a macro-conversion of an existing design, or the direct design of a circuit can be implemented using the available macros.

#### SUMMARY OF VOLUME II

Volume II is intended to include all system-specific information for each workstation supported by AMCC.

Volume II of this design manual is composed of the following sections:

|            | * VOLUMETI                                                                     |

|------------|--------------------------------------------------------------------------------|

| Section 1: | Introduction                                                                   |

| Section 2: | System-Specific Design Methodology                                             |

| Section 3: | MacroMatrix Installation and Operation Guide with system-specific design rules |

| Section 4: | Design Submission - Beyond amccsubmit                                          |

| Section 5: | RaceCheck User's Manual                                                        |

| Section 6: | MacroMatrix News - This Release                                                |

| Section 7: | Index                                                                          |

### SUMMARY OF VOLUME III

Volume III includes all generic (system independent) information and Volume III is the same regardless of the workstation supported.

Volume III of this design manual is composed of the following sections:

|             | VOLUMETII                              |

|-------------|----------------------------------------|

| Section 1:  | Introduction                           |

| Section 2:  | AMCC Schematic Rules and Conventions   |

| Section 3:  | Vector Submission Rules and Guidelines |

| Section 4:  | amccerc User's Guide                   |

| Section 5:  | amccpackage User's Guide               |

| Section 6:  | amccann User's Guide                   |

| Section 7:  | amccurc User's Guide                   |

| Section 8:  | amccsubmit User's Guide                |

| Section 9:  | AMCC Glossary                          |

| Section 10: | Index                                  |

### Workstation and System Operation; EWS-Specific Rules; Installation of the Library And Patches

Volume II of this design manual contains the Engineering-workstation (EWS) or non-schematic entry system design methodology as applicable, covering both the system-specific rules and the operational commands of the AMCC MacroMatrix support software on the specific system.

Volume II also contains the MacroMatrix Installation and Operations manualS which summarize the system-specific commands required for operation of the AMCC support software. Library and patch installation procedures are also documented. Documentation is also provided for the use of the super shell run\_amcc, Valid's run\_dir, and the sub-shells:

|                | STRIBLE     |                 |

|----------------|-------------|-----------------|

| run_amccerc    | run_amecann | run_amccpackage |

| run_amccsimfmt | run_amccvrc | run_amccsubmit  |

| run_agif       | etc.        |                 |

## **Design Validation Document**

The Design Validation document previously used by AMCC has been incorporated into *amccsubmit*. the program prompts are answered and the report submitted as part of the design submission package.

#### **Design Submission Document**

The Design Submission document has been incorporated into amccsubmit The program prompts are answered and the report submitted as part of the design submission package.

#### MacroMatrix User's Guides

Volume III contains the MacroMatrix User's Guides that detail the Engineering Rules Check (amccerc) software with error messages and probable causes; the Vector Rules Check (amccvrc) user's guide; the package selection (amccpackage) and the Annotation software and interface (amccann) user's guide; and the automated validation and submission software (amccsubmit) with a user's guide and examples.

### Glossary, Index

Volume III also presents the AMCC glossary with definitions of terms and file identification. Each volume of the design manual contains an index for that volume.

#### TRADEMARKS

The following trademarks are recognized by AMCC throughout this design (manual:

- Cadence Cadence Design Systems, Inc.

- DAZIX Daisy/An Intergraph Company

- LASAR Version 6 Teradyne, Inc.

- MacroMatrix Applied Micro Circuits Corporation (AMCC)

- Mentor Mentor Graphics Corporation

- Sun Sun Microsystems Corporation

- Valid Cadence Design Systems, Inc.

- · Verilog Cadence Design Systems, Inc.

- Synopsys Synopsys, Inc.

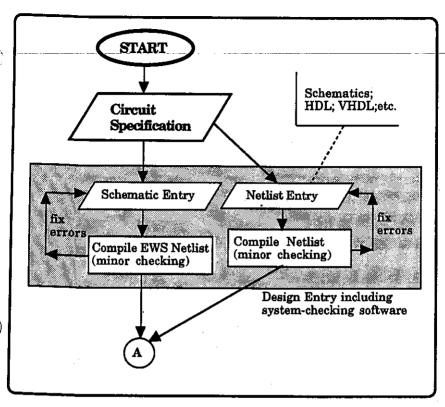

Figure 1-1a Creating the Netlist

## DESIGN SUPPORT INTERFACE

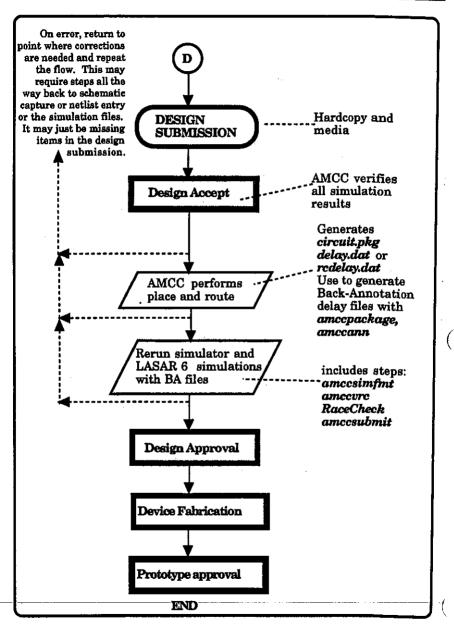

Figures 1-1a-e provide an overview of the design interface and support offered by AMCC showing the various steps required in a typical design. The basic flow is unchanged for workstation or netlist-based submissions, with the exception of the creation steps.

## Schematic Entry

Schematic entry can be performed by either the customer or by AMCC. Following schematic entry, the netlist must be generated. The netlist may be created via VHDL and other sources. If it is a netlist that AMCC software can recognize, the next step is to convert it into the AMCC Generic Interface Format or agif. The resulting netlist is called circuit.sdi. This netlist is submitted as part of the design submission package.

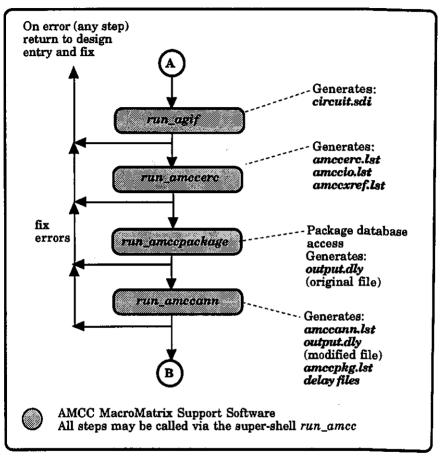

Figure 1-1b AGIF through amccann

#### AMCCERC

Following agif, the AMCC Engineering Rules Checks software (amccerc) is run.

This software performs many of the design rule checks required for design verification. The design rules for the Q20000 array series are summarized in Section 2 of this design manual.

Performing amccerc early in the design cycle clears the circuit of trivial errors, identifies loading problems (fan-out report), provides DC power computation results, checks-circuit size against-cells available by type (population report), and allows circuit clean-up before time and effort are expended on simulations. The report is named amccerc.lst and is submitted. Note that amccerc may be executed against a partial circuit capture or even a macro list (collection of unwired macros). A chip macro must exist but there are no other requirements.

Partial circuit error screening is highly recommended. It is part of structured, modular design.

amccerc produces the I/O list report, amccio.lst, which includes all pads on the array regardless of use. This report is submitted. A third report, amccxref.lst, is a cross-reference listing. It may be submitted.

### **AMCCPACKAGE**

When amccerc runs successfully, then a new software program, amccpackage is executed. AMCC has long added package delays to the annotation files. amccpackage allows the size of the package to be checked against the circuit size (new) and provides more accurate package delay information through access to the package database. It produces the datafile output.dly.

Package information for the array series is discussed in Section8 of this design manual.

### **AMCCANN**

On the completion of amccpackage, the AMCC Annotation software, amccann, is executed. amccann prepares delay files that are used during simulation. These delay files are either Front-Annotation delay or Back-Annotation delay files, depending on the existence of Place & Route data files in the directory. For a circuit which has just been captured, Front-Annotation files are produced. The report amccpkg.lst is also produced and is submitted.

amccann can produce delay files for the Dazix, Mentor and Valid native simulators as well as for Verilog and LASAR 6.

AMCC requires that simulations be performed with delay annotation files.

Timing analysis including computation of net interconnect delays using k-yactors is discussed in Section 3 of this design manual. External set-up and hold computation is discussed in Section 4.

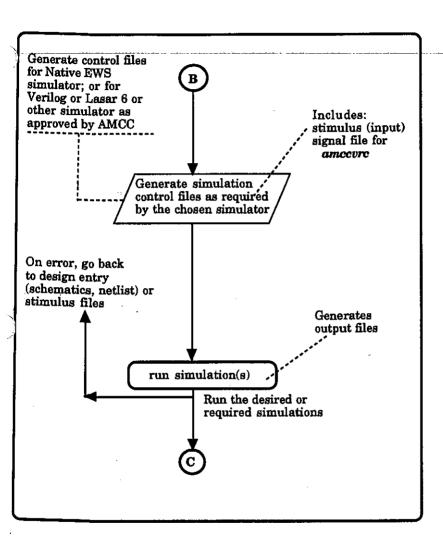

#### **Simulations**

Simulations required and vector rules and guidelines are discussed in Volume III. An overview of testing requirements is discussed in Section 10 of VOlume I.

All of the simulators which AMCC supports work with the amccann-produced delay annoation files. You must match:

Library used for simulation

Annotation file

Commands issued

The designer must develop the functional, at-speed, parametric and AC test simulation test vectors.

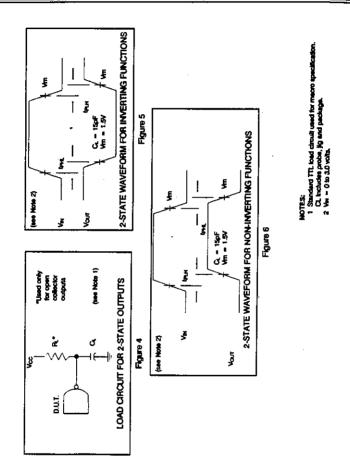

Figure 1.1c Simulations (Several are Required)

#### AMCCSIMFMT

Each simulator produces output files in a different format. Each simulation output file that is to be submitted to AMCC must be reformatted using amccsimfmt. amccsimfmt converts the list output from the simulators into the list format recognized by AMCC vector software (amccvrc, amccsubmit, RaceCheck, and Test Transfer).

${\it amccsimfmt}$  is documented in Volume II of this design manual since it is system-specific.

#### RACECHECK

For functional vectors, both fault-grading (circuit coverage) and testability analysis (hardware coverability) are recommended steps. AMCC does not provide software to support these steps although several of the workstation vendors do. AMCC uses **LASAR** 6 for Fault-Grading and will accept, on approval, fault grade scores from other simulator tools.

AMCC does provide *RaceCheck*, which performs hazard and race checking on the functional vector sets. The use of *RaceCheck* is highly recommended by AMCC. It is not currently supplied as part of MacroMatrix. Contact your AMCC representative for information on obtaining *RaceCheck* for your system.

#### AMCCVRC

The maximum delay (worst-case maximum) sampled simulation output files, after reformatting with amccsimfmt, must be processed through amccvrc, the AMCC Vector Checking software. This applies to Functional, Parametric and AC-Test simulations. amccvrc supports the rules listed in the Vector Rules and Guidelines section.

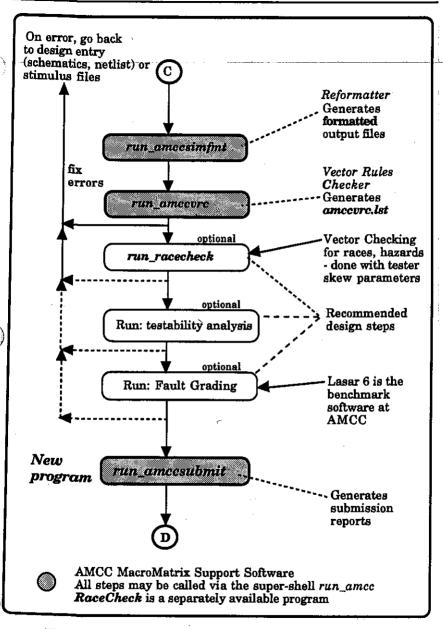

#### AMCCSUBMIT

All of the design steps and the resultant files are documented prior to submission using amccsubmit. This design submission support package replaces amcctest, which was limited to AC test submission. New with this release, amccsubmit is intended to alleviate the paperwork required in performing a design submission.

Figure 1.1d From Simulation Output Reformat to amccsubmit

Figure 1.1e Design Submission Through Prototype Approval

## Design Approval

Following design submission, AMCC Implementation or Field Application Engineers will re-execute all of the design steps and verify the design submission. They will be performed against the in-house library to ensure that the latest information on the macros is available.

#### Back-Annotation

On approval, the circuit will pass to layout using the AMCC Computer-Aided Design system, amccad. After successful layout, the Back-Annotation delay files will be available for use in simulation. AMCC performs all simulations using Back-Annotation prior to prototype authorization.

#### Simulators

Note that AMCC performs all Back-Annotated simulations using the same simulator as was chosen by the customer. This is the "sign-off" simulator.

No "golden" simulator is employed. AMCC does, however, convert all designs and test vectors into the **LASAR** 6 simulation environment for compre-hensive race and timing analysis.

LASAR 6 min-max simulation capabilities are used to identify test vector race conditions undetectable on the EWS simulator. These conditions would otherwise cause the device to fail in the actual ATE tester environment.

The test vector race conditions must be resolved prior to device fabrication.

### **Q20000 SERIES DESCRIPTION**

The AMCC Q20000 Turbo Series Logic Arrays provide an optimized systems approach to very high performance ECL semi-custom applications. Mixed-mode I/O is combined with an advanced, interactive CAD system-based design approach to provide a quick and cost-effective solution to discrete IC replacement.

The Q20P025 and Q20P010 arrays incorporate an on-chip high-frequency phase lock loop (PLL). Frequency synthesis and clock recovery macros are available for these two arrays. This array list is being expanded with the addition of the Q20P001 PLL array.

Manufacturing advantages gained from the use of the AMCC logic arrays include:

- Increased circuit density

- Increased system speed

- Reduced power

- Higher reliability

- · Lower system cost

- Operation over both military and commercial temperature ranges and power supplies

The AMCC Q20000 Turbo Series Logic Arrays Macro Library is supported on the DAZIX, Mentor Graphics and Valid Logic EWS, and the Lasar 6 simulator. Support for the Verilog logic simulator, the Synopsys Logic Synthesis System and the Cadence Design System are planned.

The designer can use any of these systems in conjunction with AMCC's MacroMatrix software package to perform schematic capture, Engineering Rules Checking (amccerc), simulation, automatic test pattern formatting (amccsimfmt), AMCC Vector Rules Checking (amccvrc), Front-Annotation and Back-Annotation (amccann) and design validation and submission assist (amccsubmit).

Simulation, amccerc error checking, amccerc rules checking, Front-Annotation and Back-Annotation are also supported on VAX/VMS systems with LASAR 6.

The Q20000 Turbo Series arrays are bipolar arrays. They can externally interface to either Schottky TTL, ECL 10K or ECL 100K. ECL 10K or ECL 100K may be standard-reference or +5V reference ECL.

As an added feature, the Q20000 Turbo Series provides the ability to mix ECL 10K and TTL or ECL 100K and TTL on the same array. ECL 10K and ECL 100K outputs are also allowed on the same array, regardless of the

ECL type used for input. For other combinations, please contact AMCC Marketing. (For specific output limits, refer to Volume I, Section 2.)

All the interface options are realized through the choice of appropriate macros, and personalized with the Metal and Via masks only.

## **Equivalent Gates - Relative Sizing**

The number of equivalent gates possible is a sizing measure for the AMCC logic arrays, used to gauge the relative sizes of different arrays. An equivalent gate is loosely defined as a 2-input NOR gate for the bipolar arrays. A measure of design density is the number of these gates that would be required to construct the design in SSI logic.

To estimate the equivalent gate counts for the Q20000 Series arrays, a 3:1 MUX with a D F/F is defined as 11 gates and a full adder as 16 gates. The number of cells required for each of these macros and the number of cells available on the array lead to the equivalent gate count.

An I/O cell can be estimated as 2 gates but is not included in either of the gate counts shown in Table 1-2.

There is no AMCCERC check for equivalent gates. Equivalent gate counts may not be used in sizing for design submission.

### Circuit Density

The actual circuit density obtained is a function of the design objectives, design approach and macros selected. The Q20000 Series uses 3-level series gating to maximize the logic density per switch.

A denser design is possible if the more complex macros are used first - start with cell-efficient, dense macros - keeping the use of SSI-level AND, OR, NOR, NAND gates to a minimum.

Designs with balanced delay path requirements use more cells than a minimized design; high-speed designs may use more cells if heavily loaded paths are to be broken up into parallel structures.

TABLE 1-2 SIZES OF THE AMCC BIPOLAR ARRAYS

| ARRAY<br>NAME                           | EQUIVA<br>GATE |            |

|-----------------------------------------|----------------|------------|

| *************************************** | MUX F/F        | Full Adder |

| . ↓                                     | METHOD         | METHOD     |

| Q20120                                  | 12500          | 17800      |

| Q20080                                  | 8000           | 11000      |

| Q20045                                  | 4500           | 6300       |

| Q20P025                                 | 2150           | 3000       |

| Q20025                                  | 2700           | 3800       |

| Q20P010                                 | 650            | 900        |

| Q20010                                  | 1000           | 1400       |

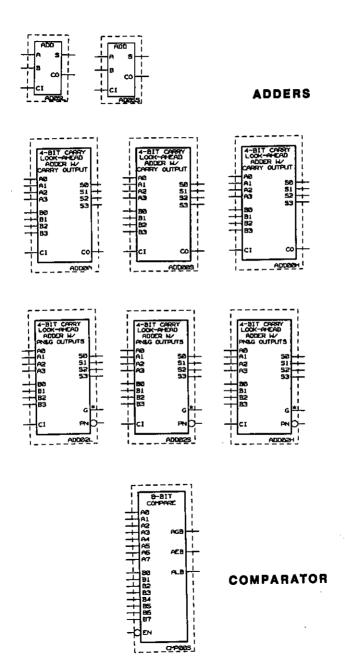

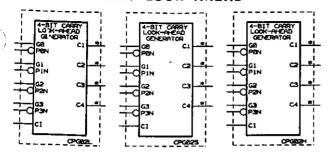

#### MACRO LIBRARY

The arrays in the Q20000 Turbo Series share a common macro function library that contains a wide selection of fully characterized logic functions varying from SSI to MSI densities. The higher functionality macros have correspondingly higher equivalent gate densities.

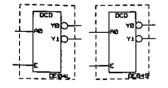

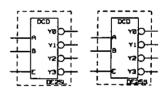

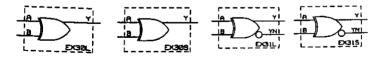

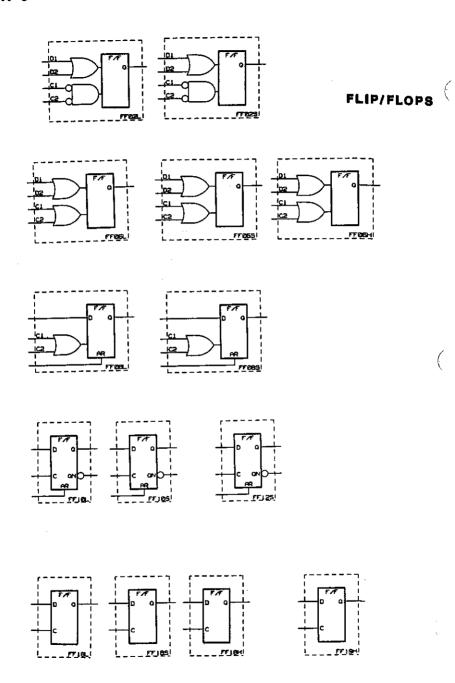

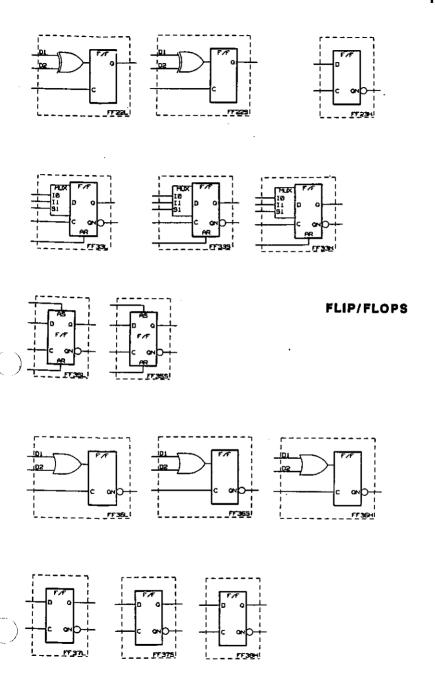

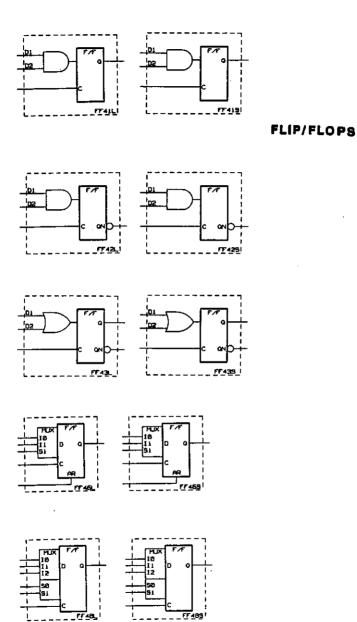

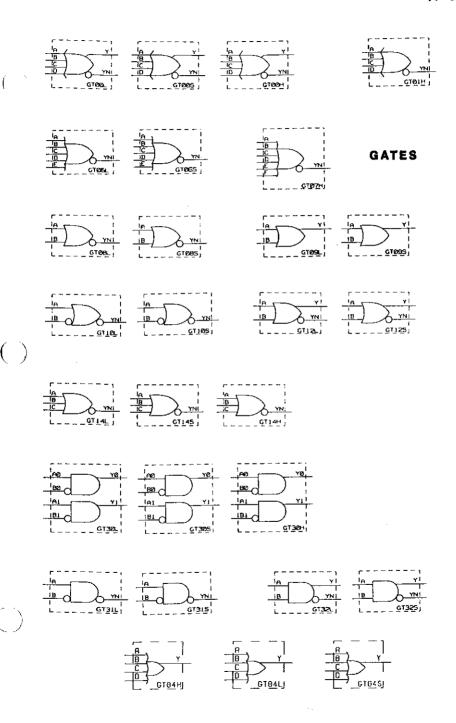

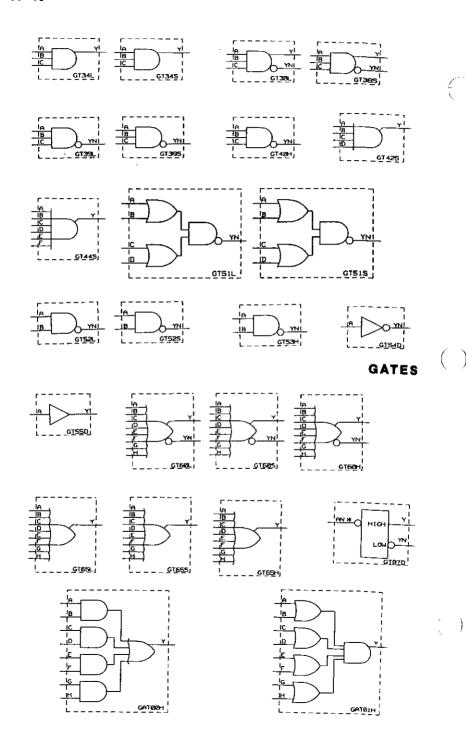

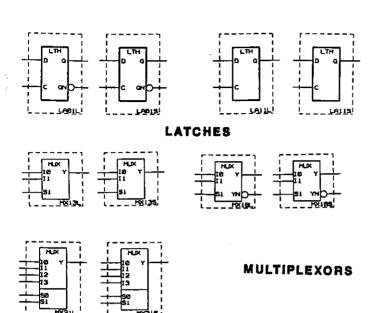

Examples of the basic logic functions include simple and complex gates, EXORs, latches, decoders, MUXs, buffered input, high-speed ECL input, buffers and output translation in the output macros, differential I/O, bidirectional I/O and 25 ohm ECL output drivers.

Many interface macros in the Q20000 Turbo Series macro library have high-speed (H) options in addition to the standard (S) option of the macro. Several macros have low-power (L) options. These macro options allow a designer to program critical paths with high-speed operation while implementing the remainder in lower power or standard-option macros.

#### TYPICAL APPLICATIONS

Typical applications include high-speed computers, graphics, communications, test equipment and instrumentation. Designed to operate in the full MIL-SPEC temperature and voltage range, the Q20000 Turbo Series also has applications in radar, EW, avionics, guidance, flight simulation and other military systems. The PLL arrays are designed for data communications, tele-communications and timing generation applications.

#### **FEATURES**

A summary of the features of the Q20000 Turbo Series includes:

On-chip high-frequency phase lock loop with edge jitter as low as 50 ps

Industry's first channelless Bipolar array

Up to 3414 internal cells

• Up to 198 I/O cells

- One micron bipolar process incorporating polysilicon emitters, trench isolation, and an advanced base emitter structure

- 3-level metal interconnection allows 100% routing at > 95% cell utilization PLL arrays up to 100%

• 3-level series gating

High-speed < 100 ps equivalent gate delays</li>

Up to 1.2 GHz Operating Frequency

• Ft = 18 GHz

High internal noise immunity

Symmetrical rise and fall times

• Ultra low power < 0.5 mW/internal gate

Speed-power programmability with S-, L- and H-options for the macros

· Power supply variation stability

Unused cells do not dissipate power

• Fully voltage- and temperature-compensated internal logic

No separate termination supply needed (e.q. -2 or -3.3V) for internal (core) operation, simplifing power supply and board design

Single cell ECL 25 and 50 ohm parallel termination drive

• Low off-chip delay penalty

• TTL, ECL 10K and ECL 100K I/O compatibility

Both ECL 10K and ECL 100K outputs may appear on the same array

Dual supply mixed ECL/TTL I/O capability

• Standard reference ECL; VEE = -5.2V or -4.5V

• +5V reference ECL

• On-chip speed monitor

• On-chip thermal diode

On-chip translators for mixed mode interface

Full CAD support, including post-autoroute and worst-case timing analysis

Autoplace and autoroute with up to 95% logic cell utilization

Supported on leading EDA tools

DAZIX Verilog (Future)

Valid Logic Lasar

Mentor Graphics

• Full Commercial and Military compatibility

# Section 2 Design Methodology

# Design Methodology

#### TECHNOLOGY

The Q20000 Turbo Series of ultra-high performance ECL/TTL logic arrays are fabricated using a one micron bipolar process incorporating trench oxide isolation (TOI) and an advanced base emitter structure.

The Q20000 Turbo Series incorporates an on-chip thermal diode pair and an on-chip AC speed monitor. These two circuits use a total of four fixed-location pads which must be connected to external package signal pins.

## ARRAY ARCHITECTURE

The Q20000 Turbo Series is the first ECL logic array family to utilize a channelless architecture called Sea-of-Cells. Using triple-layer metal, there are no dedicated routing channels between cells, allowing core density to be increased by 40%. Internal cell utilization is maintained at greater than 95% due to three layer metal interconnect and AMCC's proprietary state-of-the-art place and route system.

The AMCC logic arrays are formed from a customer-specified design added to an AMCC pre-processed silicon base array. The base arrays for the Q20000 Turbo Series are composed of two types of cells, I/O and logic cells. Each cell consists of a number of uncommitted transistors and resistors.

First level metal is used for macro intra-connect, the construction of the macro logical function from the base array components. The second and third levels of metal are used for inter-macro routing, the macro inter-connections to form the desired circuits. Power and ground distribution is also done on the first, second and third layers of metal.

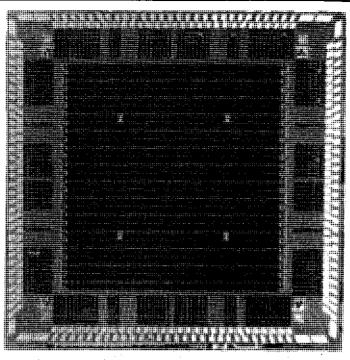

The basic cell layout of the arrays is demonstrated with the Q20080 die plot, shown in Figure 2-1. Refer to Section 7, <u>Placement</u>, for other example array die plots.

Note: placement is not to be attempted using these drawings. If a placement worksheet is required, consult AMCC Applications Engineering.

AMCC Q20080 Logic Array

Figure 2-1 Q20080 Die Plot Light squares in core area are reference generator cells. All internal core cells are called "L-cells". Groups of cells around the perimeter are the L'O cells.

#### PLL ARRAY DESCRIPTION

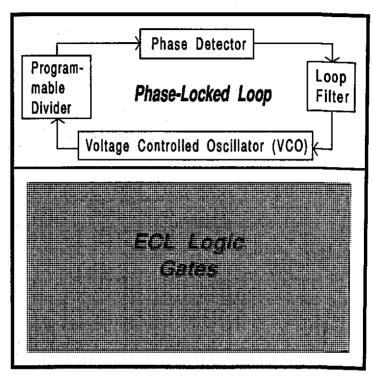

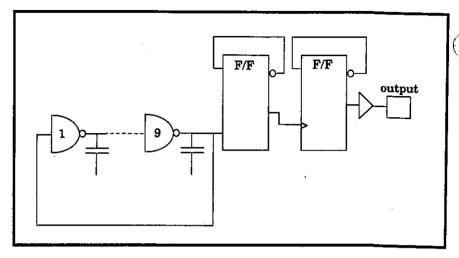

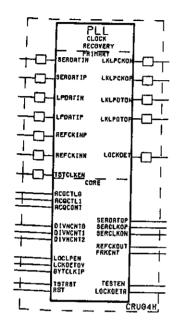

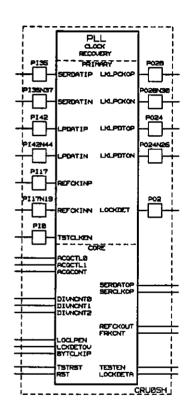

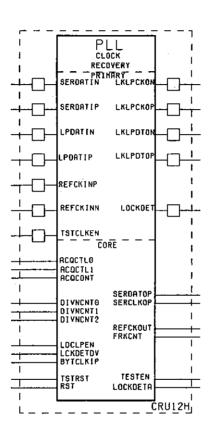

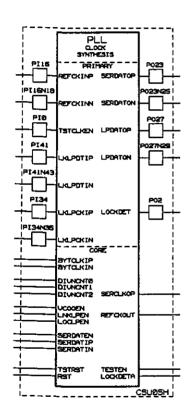

The AMCC Q20P010 and Q20P025 logic arrays are two products with densities of 928 and 3120 equivalent gates with a high frequency phase-locked loop on-chip. Combining a PLL with user-definable Q20000 series arrays, the Q20P010 and Q20P025 are tailored for high speed serial communication, video, and clock generation applications. (See Figure 2-2.)

Frequency synthesis and clock recovery macros are available for the onchip phase-locked loop. Speed options ranging from below 200MHz to 1.25GHz are available for simulation on AMCC supported engineering workstations. Lock detect, local and link loopback features are also selectable options.

For the digital logic portion of the array, an extensive library of SSI and MSI macros is available as part of the AMCC MacroMatrix design kit. Latches, parallel-to-serial converters, encode/decode functions, high speed shift registers, bit error rate computation and divide-down counters can easily be assembled to operate in conjunction with the phase-locked loop to meet specific application needs.

#### Digital Logic

The Q20000 Series is the industry's first ECL logic array family to utilize a channelless architecture called Sea-of-Cells. The Sea-of-Cells organization eliminates the dedicated routing channels between cells thereby doubling the core density. Utilization is maintained at greater than 95% due to three layer metal interconnect and the AMCC proprietary state-of-the-art place and route system. A full complement of SSI and MSI macros is offered with low power, standard and high speed options.

To insure effective operation of the Q20P010 and Q20P025, especially in low jitter applications, the digital logic must operate synchronously with the PLL.

## Phase-Locked Loop Macros

A selection of frequency synthesis and clock recovery macros are available for the on-chip phase lock loop. Speed options of 125, 132, 155, 200, 265, 311, 500, 531, 622, 1000, 1062 and 1244 MHz are selectable to operate synchronously with the logic in the digital portion of the array. Additional frequency options can be created to meet specific design requirements. AMCC defined loop filter components for each frequency option have been established for applications with divide ratios up to 64, transition densities of 30% -70%, and run lengths up to 50 bit times. For different loop filter parameters contact AMCC. Lock detect, local and link loopback features are also available options.

Figure 2-2 Phase-Locked Loop

## Encoding/Decoding

High speed datacom and telecom applications frequently require a standard encoding scheme to ensure favorable bit stream characteristics and interpoperability. AMCC initially offers two encoder/decoder schemes as standard macro options in the library. Popular in datacom applications, IBM's 8B/10B encoding scheme offers DC-balance and short run lengths in an efficiently architected implementation. Frequently used in fiber-based telecom systems, a 27-1 scrambler function is also offered. Other preferred encoding and decoding schemes can easily be designed using the digital portion of the Q20P010 and Q20P025.

## Flexible I/O Structure

The Q20P010 and Q20P025 array I/O cells are configurable to provide a flexible range of interface options. The I/O cells are designed to interface with standard (-5.2V or -4.5V) and positive reference (+5V) ECL 10KH and ECL 100K or TTL thresholds. The mixed ECL/TTL capabilities allow interface to both technologies on a single chip without the use of external translators. On-chip 50W termination is provided to facilitate low jitter interfaces. For dual power supply devices, the I/O are also capable of a Darlington-type ECL output which provides significant improvement in drive capability, toggle frequency, and power dissipation over standard ECL outputs. TTL outputs selected for use with the Q20P010 and Q20P025 must be the slower edge-rate, 8 ma type to minimize noise injection into the PLL area and should be placed on the opposite side of the chip from the PLL to the extent possible.

## ARRAY CELL RESOURCES

Table 2-1 summarizes the cell resources; Table 2-2 lists the fixed pads for the thermal diode and AC speed monitor, and Table 2-3 summarizes the power-ground resources for the Q20000 logic array series. Figure 2-2 provides a die plot for the Q20080 array.

## Turbo Driver

To overcome the power problems of conventional ECL structures, AMCC developed a patented dynamic discharge circuit in place of the traditional static current source for the emitter follower. The power requirements of Turbo macros are significantly lowered from those with conventional circuitry.

Off-chip skews for ECL 10K and ECL 100K outputs are improved as are their extrinsic  $(t_{ex})$  loading delays.

I/O cells can be configured with a Darlington output stage and Turbo to allow a single-cell 25-ohm ECL output for use on dual-power supply circuits.

TABLE 2-1

I/O AND INTERNAL CELL RESOURCES

|               |                   | I/O Cells        |                        | I/O:<br>Signals- |

|---------------|-------------------|------------------|------------------------|------------------|

| Array<br>Name | Internal<br>Cells | (för<br>signals) | I/O Cells<br>(fixed) * | PLL<br>Related   |

| Q20120        | 3414              | 198              | 4                      | N/A              |

| Q20080        | 2044              | 162              | 4                      | N/A              |

| Q20045        | 1233              | 128              | 4                      | N/A              |

| Q20P025       | 595               | 51 **            | 4                      | 12               |

| Q20025        | 733               | 100              | 4                      | N/A              |

| Q20P010       | 177               | 34 **            | 4                      | 12               |

| Q20010        | 267               | 66               | 4                      | N/A              |

<sup>\* 2</sup> pads are used by the AC Speed Monitor and 2 by the thermal diode.

Add last three colums to find total I/O cells and pads.

|               | ECL              | TIL              | PLL              | Digital          |

|---------------|------------------|------------------|------------------|------------------|

| Array<br>Name | Outputs<br>Limit | Outputs<br>Limit | Power/<br>Ground | Power/<br>Ground |

| Q20120        | 172              | 100              | N/A              | 78               |

| Q20080        | 130              | 80               | N/A              | 52               |

| Q20045        | 100              | 64               | N/A              | 52               |

| Q20P025       | 51               | 51               | 8                | 26               |

| Q20025        | 80               | 48               | N/A              | 36               |

| Q20P010       | 34               | 34               | . 8              | 20               |

| Q20010        | 50               | 24               | N/A              | 32               |

Add last two colums to find total number of fixed power and grounds.

<sup>\*\*</sup> Only for the largest arrays, 100\_LDCC for the Q20P010 and 132\_LDCC for the Q20P025

TABLE 2-2

FIXED PAD NUMBERS FOR THERMAL DIODES

AND AC-SPEED MONITOR

| ARRAY<br>NAME | THERMA<br>CATHODE PO # |     |    | D MONITOR<br>ECL*PAD * |

|---------------|------------------------|-----|----|------------------------|

| Q20120        | 207                    | 208 | 12 | 34                     |

| Q20080        | 161                    | 162 | 9  | 33                     |

| Q20045        | 136                    | 137 | 4  | 25                     |

| Q20P025       | 97                     | 93  | 3  | 26                     |

| Q20025        | 103                    | 104 | 3  | 26                     |

| Q20P010       | 88                     | 87  | 10 | 24                     |

| Q20010        | 74                     | 75  | 10 | 24                     |

TABLE 2-3

POWER-GROUND PAD RESOURCES \*

|         |                         | Q20120 | Q20080 | @20845 | G20025 | G20010 |

|---------|-------------------------|--------|--------|--------|--------|--------|

|         | E: TOTAL * * PWR/ GNDS: | 78     | 52     | 52     | 36     | 32     |

| 100%    | core GND (*)            | 20     | 16     | 16     | 8      | 8      |

| ECL,    | core V- (**)            | 18     | 16     | 16     | 8      | 8      |

| single  | I/O GND (*)             | 40     | 20     | 20     | 20     | 16     |

| supply  |                         |        |        |        |        |        |

| 100%    | CORE GND (0V)           | 20     | 16     | 16     | - 8    | 8      |

| ECL     | CORE V- (**)            | 18     | 16     | 16     | . 8    | 8      |

| dual    | I/O V+ (+5V)            | 8      | 4      | 4      | 4      | 4      |

| supply  | I/O GND (0V)            | 32     | 16     | 16     | 16     | 12     |

|         | CORE GND (0V)           | 20     | 16     | 16     | 8      | 8      |

| MIX,    | CORE V- (**)            | 18     | 16     | 16     | 8      | 8      |

| dual    | I/O V+ (+5V)            | 8      | 4      | 4      | 4      | 4      |

| supply  | I/O GND (0V)            | 32     | 16     | 16     | 16     | 12     |

| ECL/TTL | CORE GND (0V)           | 18     | 16     | 16     | 8      | 8      |

| MIX,    | CORE V+ (+5V)           | 20     | 16     | 16     | 8      | 8      |

| single  | I/O V+ (+5V)            | 28     | 16     | 16     | 16     | 12     |

| supply  | I/O GND (0V)            | 12     | 4      | 4      | 4      | 4      |

<sup>\*</sup> For a detailed list, see AMCCIO.LST

| TABLE 2-3                  |           |  |  |  |

|----------------------------|-----------|--|--|--|

| POWER-GROUND PAD RESOURCES | CONTINUED |  |  |  |

|                           | (020F025) | G202010 |

|---------------------------|-----------|---------|

| VO MODE: TOTAL PWRV GNDS: | 47        | 30      |

| ECL/TTL CORE GND (0V)     | 10        | 6       |

| MIX CORE V- (**)          | 16        | 11      |

| DUAL 1/O V+ (+5V)         | 2         | 2       |

| SUPPLY I/O GND (0V)       | 19        | 11      |

| ECL/TTL CORE GND (0V)     | 10        | 6       |

| MIX CORE V+ (+5V)         | 16        | 11      |

| SINGLE I/O V+ (+5V)       | 19        | 11      |

| SUPPLY I/O GND (0V)       | 2         | 2       |

<sup>\*\*</sup> CORE V: -5.2V for STD-REF ECL 10K -4.5V for STD-REF ECL 100K 0V for +5V-REF ECL 10K or ECL 100K

## Macro Configuration

A customer design is described via schematics using the macros contained in the released library for the array series. Macros are individually configured in an array by interconnecting the components within a cell with the first layer metal to form the customer-selected macro functions. Macro placement is performed automatically by the AMCC proprietary CAD software (amccad).

## Interconnections and Routing

Interconnections between macros (routing) use both the second and third layers of metal, following specific routing tracks. Routing is performed automatically by AMCC proprietary CAD software.

<sup>\*</sup> CORE GND: 0V for STD-REF ECL 10K or ECL 100K +5V for +5V-REF ECL 10K or ECL 100K

Additionally, the AMCC CAD software has been designed to automatically transform a logic design implemented in AMCC macros into an efficient high performance layout design. If there are sensitive timing and/or skew constraints, AMCC can optionally offer preplacement of the macros implementing these critical areas.

The customization of the array is performed by adding the 3-layer metal interconnect, representing the macros and their interconnection, to the base array.

#### Logic Cells

The internal logic cells are organized to support high-level logic functions such as latches, multiplexors, decoders, etc. Simple and complex gates can also be made from these cells. The internal cells (L cells) support the Turbo circuitry, allowing internal Turbo macros to support an 18-load fan-out load limit.

#### I/O Cella

The interface to the arrays is accomplished in the input/output cells on the Q20000 Turbo Series Logic Arrays. The I/O cells are located around the perimeter of the array. For all arrays, ECL- and TTL-translators and most of the required buffers are included in the I/O cells for external interfacing to both ECL and TTL. Each individual I/O cell is configurable to be either TTL, ECL 10K or ECL 100K.

## Overhead Circuitry

In addition to the cells, each array contains overhead circuitry: bias generators, voltage references and voltage regulators. Overhead circuitry is predefined by AMCC.

## MACRO PAD NAMES - CHANGES

AMCC has changed its naming conventions for macro input and output pad names. Instead of "PAD", look for PI, PI2N, PO, PON and variations to indicate input, inverting input with more than one input on the macro, output, and inverting output respectively. Designers with designs-in-progress at this release will need to update their schematics.

#### INTERFACE OPTIONS

The array itself can be configured to be 100% ECL 10K, 100% ECL 100K, TTL/ECL 10K or TTL/ECL 100K, with dual power supplies, or 100% ECL or TTL/ECL 10K or TTL/ECL 100K with a single +5V supply. (See Table 2-4.) In addition, both ECL 10K and ECL 100K outputs may be used on any given array. Only one type of ECL is allowed for input, defined by the chip macro.

## TABLE 2-4 POWER SUPPLY OPTIONS\*

| 2.35%         | PO  | -SINGLE<br>Wer Supi | oly . |           | AL<br>SUPPLY |

|---------------|-----|---------------------|-------|-----------|--------------|

|               | +5V | -5.2V               | -4.5V | +5V/-5.2V | +5V/-4.5V    |

| 100% ECL 10K  | Y   | Y                   | Y     | Υ         | Υ            |

| 100% ECL 100K | Υ   | Υ                   | Υ     | Y         | Υ            |

| ECL 10K/TTL   | Υ   | _                   |       | Y         |              |

| ECL 100K/TTL  | Υ   | _                   | _     | Υ         | Υ            |

\* ECL 10K can be operated at ECL 100K voltages and visa versa; consult AMCC concerning DC parametrics. For 100% TTL, consult AMCC

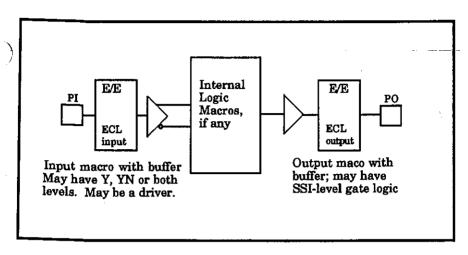

#### Interface Guidelines

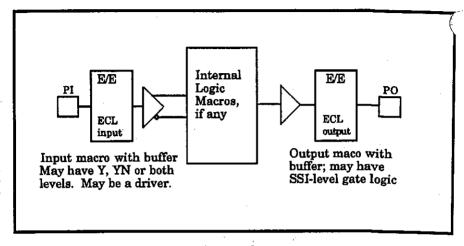

A summary of the interface guidelines for the three I/O modes of operation is shown in Figure 2-3. Most of the I/O macros for the Q20000 Turbo Series include buffer functions, to simplify I/O selection. The designer should review the I/O options to determine where these options would enhance the circuit efficiency.

Figure 2-3a

Q20000 Series Interface Macro Guidelines

100% ECL Interface

Dual +5V And -5.2V

Or +5V And -4.5V Power Supplies

DECL

- Use ECL interface macros (IExx, UExx, UKxx)

- ECL input macros contain buffers

- Same macro for either +5V/-5.2V or +5V/-4.5V paring

- Use ECL interface macros (OExx, OKxx, UExx, UKxx)

- ECL available to drive 50 ohm and 25 ohm off-chip terminations

- ECL output macros contain necessary buffers

- Supports both ECL 10K (OExx, UExx) and ECL 100K (OKxx, UKxx)

- Supports single-cell 25 ohm output

- Supports Darlington outputs

Figure 2-3b

Q20000 Series Interface Macro Guidelines

100% ECL Interface

-5.2V -4.5V Or +5V

Single Power Supply

- Use ECL interface macros (IExx, UExx, UKxx)

- ECL input macros contain buffers

- Same macro for either +5V, -5.2V or -4.5V single supply

- Use ECL interface macros (OExx, OKxx, UExx, UKxx)

- ECL available in 50 ohm and 25 ohm

- ECL output macros contain necessary buffers

- Supports both ECL 10K (OExx, UExx) and ECL 100K (OKxx, UKxx)

- Does NOT support single-cell 25 ohm output

- Supports 2-cell 25 ohm output

- Does NOT support Darlington outputs

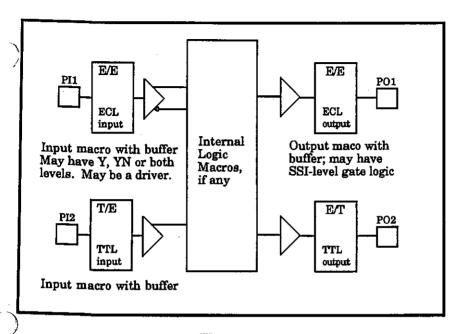

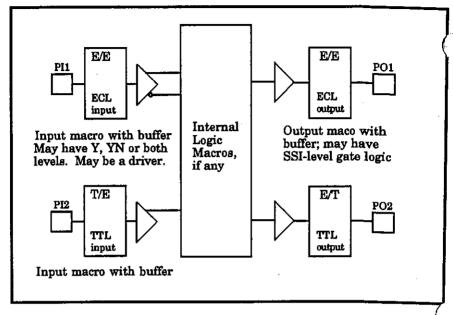

Figure 2-3c Q20000 Series Interface Macro Guidelines Mixed ECL/TTL Interface Dual +5V and -5.2V or +5V and -4.5V Power Supplies

- Use TTLMIX interface macros for TTL (ITxx, UTxx)

- Use ECL interface macros (IExx, UExx, UKxx)

- Input macros contain buffers

- Same macro for either +5V/-5.2V or +5V/-4.5V power supply paring

- Use TTLMIX interface macros for TTL (OTxx, UTxx)

- Use ECL interface macros (OExx, OKxx, UExx, UKxx)

- ECL available in 50 ohm and 25 ohm

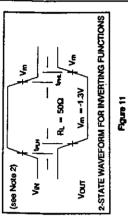

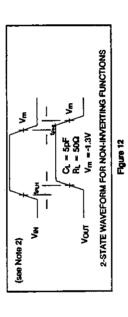

- Output macros contain necessary buffers