# Design Validation Review Bipolar Arrays

**BIPOLAR**

#### DESIGN VALIDATION

The following is a listing of the design checks that <u>must be</u> made prior to submitting a design to AMCC for the final design review. A design validation review is required for all designs done with the aid of the DAISY, MENTOR, VALID, CAE, etc. or TEGAS V EWS systems.

The AMCC design validation software, also known as the ERC software, performs many of these checks and creates various output files that list the flagged errors and supply valuable design documentation. In many cases, the process of reviewing the ERC output files and redesigning to remove errors flagged will increase the probability of a buildable, testable, successful circuit. AMCC recommends that the designer review this list before starting a design.

On the following pages, [ ERC ] is used to indicate that a check is performed by the AMCC proprietary design validation software. [ FUTURE ERC ] is used for those checks that must be performed manually at present, but which will be automated within the next quarter.

Where an ERC check is not available (usually due to the design-dependence of the problem area), then the check cannot be programmed. The flag [ MANUAL ] is used to indicate when a check must be performed by the designer.

- o ERC sofware is available for the DAISY engineering workstations. While it is currently executed on the VAX due to 8086 limitations on the LOGICIAN, it will soon be available on the DAISY 80286-based LOGICIAN.

- o ERC software is available for the MENTOR and the VALID engineering workstations where it is system-resident.

- o ERC software is available for TEGAS V netlist designs.

A special file called AGIF (AMCC Generic Interface File) is used to transfer a design from the EWS to the VAX for ERC support, test development (TEGAS), fault-grading and layout. This file is created by AMCC support software on the individual workstation and the EWS-VAX interface is unique to each workstation.

Reference: Internal array resources, cell utilization, pin count limits for routability, array I/O resources as listed in the design guide.

#### CELL COUNT

O CELL COUNT (POPULATION) MUST NOT EXCEED THE ARRAY LIMITS FOR ANY CELL TYPE

(I,O,I/O,L,B). [ ERC ]

O THE CELL UTILIZATION (L, B CELLS) MUST NOT EXCEED THE ARRAY LIMITS. [ ERC ]

#### INTERNAL PIN COUNT

- O THE PIN COUNT (NUMBER OF INTERNAL PINS THAT MUST BE ROUTED) MUST NOT EXCEED THE LIMIT FOR THE ARRAY [ ERC ]

- o COMPUTE THE ACTUAL OR ESTIMATE THE PIN COUNT refer to the design guide if you are estimating the pin-count. Q700: the designer must temporarily add the threshold generator connections to the pin count generated by ERC.

[ ERC OR MANUAL CHECK ]

- O BY EWS CONVENTION, UNUSED MACRO INPUT PINS ARE GROUNDED ON THE SCHEMATIC (THEY FLOAT IN REALITY) [ ERC ]

- O BY EWS CONVENTION, UNUSED MACRO OUTPUT PINS ARE TERMINATED (DO NOT WIRE-OR THE TERMINATED OUTPUTS TOGETHER) [ ERC ]

Reference: Macro summary section of the appropriate design guide.

### PIN RESTRICTIONS (ANY)

O ANY MACRO WITH AN ASTERISK HAS A PIN-RESTRICTION OR NOTATIONAL COMMENT IN THE DESIGN GUIDE - HAVE THESE BEEN HONORED? [ ERC ]

#### NAMING

o SEE THE AMCC SCHEMATIC RULES [ ERC ]

## I/O PLACEMENT (CUSTOMER GENERATED) (OPTIONAL)

O HAS A PLACEMENT REQUEST BEEN SUBMITTED TO AMCC FOR APPROVAL?

## BONDING DIAGRAM (OPTIONAL)

O HAS ONE BEEN COMPLETED AND SUBMITTED TO AMCC FOR APPROVAL?

#### MACRO CHECK (REQUIRED)

- o WAS A MACRO LIST TURNED OVER TO AMCC? [ ERC ]

- O ARE ALL OF THE MACROS USED IN THE DESIGN APPROVED BY AMCC, i.e., FROM AN OFFICIAL RELEASE OR PATCH? [ ERC AT AMCC AFTER DESIGN SUBMISSION ]

Reference: I/O interface sections of the appropriate design guide.

#### 1/0

- O THE I/O SIGNAL COUNT MUST NOT EXCEED THE LIMITS FOR THE ARRAY. [ ERC ]

- O I/O SIGNAL, POWER AND GND COUNT MUST NOT EXCEED THE ENTIRE PACKAGE LIMIT. [ MANUAL CHECK ]

- O TO IMPROVE NOISE MARGIN AND OPERATIONAL RELIABILITY, ADDITIONAL I, O OR I/O CELLS MUST BE USED AS V<sub>CC</sub> AND GROUND PADS UNDER CERTAIN CONDITIONS. HAS THE APPROPRIATE DESIGN GUIDE BEEN REFERENCED FOR THESE CONDITIONS? [ MANUAL CHECK ]

- O EACH TTL OUTPUT MACRO WITH DIFFERENTIAL INPUTS MUST BE DRIVEN BY TRUE AND COMPLEMENT OUTPUTS COMING FROM THE SAME MACRO. ARE THEY? [ MANUAL CHECK ]

- O ANY LOADING ON THESE DIFFERENTIAL LINES SHOULD BE BALANCED. IS IT? [ MANUAL CHECK ]

- O DRIVING MACROS FOR THESE DIFFERENTIAL INPUTS SHOULD NOT HANDLE MORE THAN THREE ADDITIONAL LOADS. [ MANUAL CHECK ]

- O Q700: TTL AND TTLMIX INPUT BUFFERS: ALL INPUTS MUST BE USED (NO INPUTS MAY BE GROUNDED) [ ERC ]

- O DIFFERENTIAL ECL INPUT IS ACCOMPLISHED WITH TWO INPUT MACROS AND ONE DIFFERENTIAL BUFFER. HAS THE PROPER BUFFER BEEN USED?

[ MANUAL CHECK ]

- O ECL 10K AND ECL 100K CANNOT APPEAR ON THE SAME ARRAY

- O HAVE ALL I/O SIGNALS BEEN IDENTIFIED AS TO TYPE (ECL, TTL)?

[ MANUAL CHECK ]

ECL: SPECIFY TERMINATION (50ohm, 100ohm, 200ohm)

TTL: SPECIFY IF 3-STATE, OPEN-COLLECTOR, BIDIRECTIONAL

O DO THE MACROS SELECTED MATCH WHAT IS DOCUMENTED ABOVE?

[ MANUAL CHECK ]

Reference: Macro summary section of the appropriate design guide.

#### THRESHOLD GENERATORS

- O USE THE CORRECT THRESHOLD GENERATORS WHERE APPLICABLE (VTA FOR THE BIXX MACROS, Q1500 AND Q3500 SERIES) [ ERC ]

- o FOR THE Q700 SERIES, Q1500 SERIES, DO NOT EXCEED THE VTI LOADING WHEN USING TTL HIGH-SPEED INPUT MACROS [ ERC ]

- O THRESHOLD GENERATOR PINS WHICH DO NOT APPEAR ON THE MACRO GRAPHIC SYMBOL ARE TO BE COUNTED IN THE ARRAY PIN COUNT FOR THE Q700 SERIES. AT PRESENT, REFER TO THE DESIGN GUIDE.

[ FUTURE ERC ]

#### ECL OUTPUT BUFFERS

o USE THE CORRECT DRIVE CAPABILITY FOR THE ECL OUTPUTS (50, 100, 200 OHMS) [ MANUAL CHECK ]

O DO NOT EXCEED THE ECL OUTPUT BUFFER LIMIT FOR THE I/O MODE AND ARRAY (Q700, Q1500 SERIES) - ECL OUTPUTS ARE LIMITED BY B CELLS AND PINS AVAILABLE [ MANUAL CHECK ]

Reference: Cell utilization, I/O interface sections of the appropriate design guide.

### BUFFERS - GENERAL

- O BUFFERS REQUIRED FOR INPUT (OR OUTPUT) MUST BE CONSIDERED WHEN MAKING A CELL COUNT. [ ERC ]

- O CHECK THE MATCH OF THE TTL INPUTS AND THE TTL BUFFERS (PIN RESTRICTIONS) FOR THE Q700 SERIES IN PARTICULAR [ ERC ]

- O MAKE CERTAIN THAT THE I/O MACROS DRIVE THE CORRECT BUFFER, AND THAT THE BUFFERS ARE DRIVEN BY THE CORRECT I/O MACROS [ ERC ]

Reference: Macro summary section of the appropriate design guide.

#### CIRCUIT I/O MODE

- O USE A BORDER ON ALL SCHEMATICS [ ERC ]

- O CHECK FOR MACRO COMPATIBILITY ARE YOU MIXING TYPES (TTL, TTLMIX, ECL 10K, ECL 100K, +5V REF ECL) WHEN YOU ARE NOT SUPPOSED TO BE DOING SO? [ ERC ]

Reference: Fanout tables for maximum and derated loading on macros by option and classification; tpd+ and tpd- tables in the design guide section on computing propagation delay.

#### FANOUT

- O OBSERVE FANOUT RULES FOR THE MACROS SELECTED [ ERC ]

- O CLOCK AND OTHER DISTORTION/SPEED SENSITIVE PATHS WILL USE MACROS WITH 20% DERATED LOADING LIMITS [ MANUAL CHECK ] (REFER TO MACROCCUR TABLE GENERATED BY THE ERC PROGRAM)

Reference: Wire-OR tables for maximum wire-OR loading on macros by option and classification; tpd+ and tpd- tables in the design guide section on computing propagation delay.

#### WIRE-ORS

- O WIRE-ORS MAY NOT HAVE MORE THAN 4 INPUTS IF THEY DO, RE-DESIGN THEM. [ ERC ]

- O NEVER CASCADE WIRE-ORS (FEED THE OUTPUT OF ONE INTO THE INPUT OF ANOTHER) [ ERC ]

- O DO NOT WIRE-OR DRIVER MACROS (THREE-STATE ENABLE DRIVERS OR HIGH FANOUT DRIVERS) [ FUTURE ERC ]

- O DO NOT WIRE-OR LATCH OUTPUTS UNLESS THEY ARE SPECIFICALLY ALLOWED [ ERC ]

- O DO NOT WIRE-OR MACROS WHOSE FANOUT LOADING IS RESTRICTED TO 1 (SUCH AS UNBUFFERED INPUT MACROS, OUTPUT BUFFER MACROS) [ ERC ]

- O DO NOT GROUND ANY WIRE-OR INPUT PINS (AND ALL INPUT PINS MUST BE USED) [ ERC ]

- O USE COMPONENT WIRE-ORS. THEY INCLUDE tpd+ and tpd- PARAMETERS. MENTOR, VALID, TEGAS V ALSO SUPPORT PARAMETRIC WIRE-ORS. [ MANUAL CHECK ]

- O DO NOT USE DAISY PARAMETRIC WIRE-ORS. (THEY DO NOT SUPPORT THE TIME PARAMETERS.) [ MANUAL ]

Reference: Macro summary section of the appropriate design guide.

#### THREE-STATE ENABLE - THREE-STATE ENABLE-DRIVER

- O DRIVE THE THREE-STATE ENABLE PIN ON THREE-STATED MACROS BY A SPECIAL THREE STATE ENABLE DRIVER.

- O USE ONE THREE-STATE ENABLE-DRIVER MACRO FOR LOADS UP TO 8 [ ERC ]

- O USE MULTIPLE "INTERNALLY" SOURCED THREE-STATE ENABLE-DRIVER MACROS FOR HIGHER LOADS OR WHERE THE SIGNAL IS INTERNALLY GENERATED. [ ERC ]

- O CAN INTERNALLY-GENERATED THREE-STATE ENABLES BE MONITORED DURING TEST? CAN THEY BE DISABLED AND THE ENABLE SIGNAL DRIVEN EXTERNALLY DURING TEST?

#### MASTER-SLAVE F/F - Q700

- O USE THE SPECIAL CLOCK DRIVER (EF370, EF371 OR EF372) FOR THE MASTER-SLAVE FLIP/FLOP (EF720, EF730) ON A Q700 DESIGN [ ERC ]

- O USE A COMMON CLOCK FOR THE MASTER AND SLAVE F/F IMPLEMENTATION LATCHES. [ MANUAL CHECK ]

Reference: Appropriate design guide.

#### CLOCK [ MANUAL CHECK ]

- O MACRO SELECTION, MACRO PREPLACEMENT, AND PREROUTING OF WIRING IS DEPENDENT ON THE CRITICAL PATHS AND/OR THE MAXIMUM FREQUENCY REQUIREMENTS.

- O ALL CRITICAL AND SENSITIVE PATHS IN A CIRCUIT MUST BE IDENTIFIED AND THE CRITICAL PATH(S) TIMING COMPUTED.

- O CALCULATE THE CRITICAL PATHS UNDER WORST-CASE CONDITIONS, FOR BOTH RISING AND FALLING EDGE INPUT

- O COMPUTE ASYMMETRICAL (RISING EDGE, FALLING EDGE) PROPAGATION

- O DESIRED SET-UP AND HOLD TIMES MUST BE LISTED

- O PERFORMANCE AT MAXIMUM FREQUENCY MUST BE LISTED.

- O KEEP THE MAXIMUM CLOCK FREQUENCY WITHIN LIMITS FOR THE ARRAY AND I/O MODE

- O INVERT THE MACRO OUTPUTS (SWITCH POLARITY OF THE SIGNAL) TO MINIMIZE PULSE SHAPING (PULSE STRETCH AND PULSE SHRINK) BALANCE THIS AGAINST ASYMMETRICAL INPUT MACROS IN A TTL DESIGN

#### CLOCK (CONTINUED) [ MANUAL CHECK ]

- O CHECK FOR RACE CONDITIONS IN THE DESIGN (USE DAISY DTA, DTV, TEGAS V OR OTHER SIMULATOR RUNNING AT SPEED WITH TIMING CHECKS ENABLED. AUGMENT WITH ADDITIONAL CALCULATIONS.)

- O SIMULATE THE DESIGN FOR BOTH NORMAL AND WORST CASE CONDITIONS AND COMPARE THE RESULTS (THERE SHOULD BE A FUNCTIONAL MATCH)

- O AVOID CLOCK SKEWING BY PRE-PLACEMENT AND BALANCED LOADING

- O DERATE THE LOADING LIMITS ON ALL MACROS IN A CLOCK PATH

- O SPECIAL REQUIREMENTS, SUCH AS UNUSUAL LOADING AND SIGNAL BALANCING MUST BE REQUESTED IN WRITING.

Reference: Section on power dissipation, maximum current specification in the appropriate design guide.

#### POWER CONSIDERATIONS

- O COMPUTE THE WORST-CASE POWER (ERC AND MANUAL EFFORT)

- O COMPUTE THE WORST CASE MAXIMUM CURRENT FOR THE INTERNAL ARRAY (L, B CELLS) [ FUTURE ERC ]

- O DURING LAYOUT MAXIMUM ROW AND HALF-ROW CURRENT SPECIFICATIONS APPLY AND ARE CHECKED BY DESIGN RULES CHECKING SOFTWARE [ DRC ]

- O HAS THE MAXIMUM CURRENT BEEN EXCEEDED FOR THE INTERNAL PART OF THE ARRAY? [ FUTURE ERC ]

- O UNUSED CELLS DRAW NO CURRENT

- O THE <u>FULL CURRENT</u> IS DISSIPATED FOR A MACRO <u>EVEN</u>

IF IT IS ONLY PARTIALLY USED

- CURRENT SOURCE REDUCTION IS A CUSTOM OPERATION

#### TESTABILITY CHECKS [ MANUAL CHECK ]

- O CAN ALL SEQUENTIAL CIRCUITS BE INITIALIZED? (100 STEPS MAX; PREFER FASTER SET-UP) USE RESET/SET LOGIC ELEMENTS WHENEVER POSSIBLE; LATCHES FOR TRANSPARENCY; ETC.

- O ARE ANY COUNTERS > 8 BITS LONG? LIMIT COUNTER CHAINS TO 256 STEPS MAXIMUM OR BREAK THEM UP.

- O ARE ANY UNUSED PADS/PINS AVAILABLE TO IMPROVE CONTROLLABILITY OR OBSERVABILITY? HAVE THESE BEEN USED FOR TEST POINTS?

- O HAS THE COMBINATIONAL LOGIC BEEN MINIMIZED TO REMOVE REDUNDANCY? (REDUCES FAULT MASKING IF CIRCUIT IS MINIMIZED)

- O ARE INTERNAL SIGNALS NAMED FOR INCLUSION IN THE FORMAT FOR THE TEST FILE AS DESIRED?

#### SIMULATION VECTOR CHECKS [ MANUAL ]

#### FUNCTIONAL SIMULATION

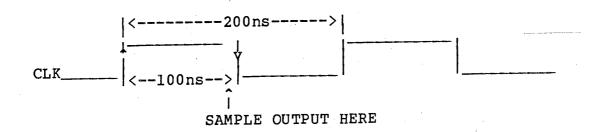

O 100ns CLOCK EDGE IS THE MINIMUM. THE FAIRCHILD SENTRY TESTER IS USED WITH A MAXIMUM FREQUENCY OF 5MHz STEP THROUGH RATE.

- O THE SIMULATION "PAGE" CANNOT EXCEED 4000 STEPS CONCATENATED FROM SMALLER SIMULATION VECTOR SETS.

- O SENTRY TESTER MEMORY SIZE LIMIT

- O EACH "PAGE" MUST BEGIN WITH INITIALIZATION

- O EACH "PAGE" MUST CONTAIN INITIALIZATION EVERY 1000 STEPS, AT A MINIMUM

- O HP TESTER MEMORY SIZE LIMIT

(FOR THE HP TESTER SHOULD DEBUG BE REQUIRED

THE HP PAGE IS 1200 VECTORS)

- O ALL INPUTS MUST BE SET TO "1" OR "0" ON THE FIRST TIME STEP (CLOCK = 0)

(SET BIDIRECTIONALS TO HIGH-Z - THE TESTER CANNOT ACCEPT "X" - HIGH-Z MAY BE USED ON INPUTS)

- O THE FIRST PAGE SHOULD BEGIN WITH A SIMULATION SEQUENCE THAT SWITCHES EACH INPUT AND EACH OUTPUT FROM 0-1 AND FROM 1-0. THIS REQUIREMENT IS FROM TEST AND IS FOR CONNECTIVITY CHECKING PRIOR TO OPERATIONAL TESTING.

- O UNINITIALIZED OUTPUTS SHOULD BE SHOWN AS "X" OR "U"; NON-BOOLEAN OUTPUTS (EXCEPT HIGH-Z FOR THREE-STATED OUTPUTS) ARE NOT ALLOWED.

- O THE SIGNAL OR STATES CONTROLLING BIDIRECTIONAL SIGNALS MUST BE CLEARLY DEFINED ARE THEY?

- O BIDIRECTIONAL I/O IS TESTED WITH TWO STEPS TO ASSURE TIME TO ACHIEVE THE DIRECTIONAL SWITCH TWO STEPS ARE REQUIRED TO CHANGE THE DIRECTION OF A BIDIRECTIONAL SIGNAL ONE FOR DIRECTION, ONE FOR THE SIGNAL

- O IF A THREE-STATE ENABLE SIGNAL IS GENERATED INTERNALLY, IT MUST BE NAMED AND LISTED IN THE DAISY FORMAT FILE (MENTOR, VALID, TEGAS FILES) SO THAT THE OUTPUT PORTION OF THE SIMULATION VECTORS SHOW THE PROPER STATE FOR THE ENABLE(S). IF IT IS DESIREABLE TO CONTROL THIS SIGNAL, APPROPRIATE DEGATING LOGIC AND INPUT MACROS MUST BE ADDED.

- o FOR FILES WITH LONG SIMULATION SEQUENCES (IN EXCESS OF 1000 STEPS):

- THESE SHOULD BE PLACED AT THE END OF THE TEST FILE, IF POSSIBLE, TO ALLOW MODULAR BREAKDOWN OF THE TEST SET AND TO MINIMIZE POTENTIAL DEBUG PROBLEMS.

- O HEAVY SWITCHING I/O

- SHOULD BE RUN AT THE END OF THE SIMULATION.

- O HAVE SIMULTANEOUS CHANGES OF CLOCK AND DATA BEEN ELIMINATED?

- O MULTIPLE-SIGNAL-GENERATED CLOCKS HAVE SIMULATANEOUS CHANGES OF THESE SIGNALS BEEN ELIMINATED?

- O HAS THE METHOD FOR THE SIMULATION FILE(S) GENERATION BEEN DOCUMENTED? (VIEW, RUN, START, ETC. FOR THE DAISY FOR EXAMPLE, COMPRABLE PROCEDURES FOR THE OTHER EWS SYSTEMS.)

- O WAS THE PRINT\_ON\_CHANGE (DAISY) OR COMPRABLE OUTPUT FILE REQUESTED FOR EVERY SIMULATION RUN?

- O WAS THE SAME FORMAT FILE USED FOR ALL SIMULATION VECTORS? (ALL VECTORS SHOW BIT 1 IS THE SAME SIGNAL, ETC.)

- O WAS 100ns THE STEP AND DOES THE SAMPLE START AT 99ns (i.e., for DAISY, VIEW 999 1000) SO THAT THE SIMULATION VECTORS ARE PAIRED WITH THEIR EXPECTED OUTPUT? (THE BIT VECTORS ARE USED TO FORM STAND ALONE TEST PATTERNS)

- O ARE THE FILES COMMENTED WITH COMPANY, DESIGNER, CIRCUIT NAME, DATE, AND A DESCRIPTION OF THE TESTING BEING PERFORMED? (STRUCTURED PROGRAMMING)

- o ARE THE FILES ON AMCC-READABLE MEDIA?

#### AT SPEED SIMULATION REQUIREMENTS [ MANUAL CHECK ]

- O HAS A SIMULATION BEEN PERFORMED "AT SPEED"?

- O IS THE SCALING CORRECT FOR THE ARRAY?

(THERE ARE TWO SCALES IN USE; 1 = 0.1ns (1000 = 100ns) FOR THE Q700 AND Q1500 SERIES ARRAYS; 1 = 0.01ns (10000 = 100ns) FOR THE Q3500 SERIES ARRAYS)

- O THE SAME RULES APPLY AS FOR FUNCTIONAL SIMULATION

The customer should be aware that the output states may not be well settled within the available vector period, and that the apparent "phase delay" of some outputs relative to others makes the evaluation of "at-speed" simulation results a non-trivial exercise.

AMCC is prepared to assist the customer in interpreting and understanding the results of such simulation.

OTHER TESTING (OPTIONAL) [ MANUAL CHECK ]

o ARE ADDITIONAL TESTS REQUIRED?

# STANDARD AC TEST (PACKAGED PARTS ONLY)

- O PROPAGATION DELAY ONLY, MEASURED FROM ONE INPUT TO ONE OUTPUT

- O HAVE THE PATHS BEEN SPECIFIED?

- O SIMULATION VECTORS MUST BE IN THE PROPER FORMAT FOR AMCC SIMULATOR AND THE "CARE" (AS OPPOSED TO "DON'T CARE") VECTORS MUST BE DEFINED

- O VECTORS FOR EACH PATH MUST BE SELF-INITIALIZING (STAND-ALONE)

- O LIMITED TO TEN PATHS (20 MEASUREMENTS) FOR ARRAYS WITH LESS THAN 2,000 EQUIVALENT GATES; TO 20 PATHS (40 MEASUREMENTS) FOR ARRAY WITH MORE THAN OR EQUAL TO 2,000 EQUIVALENT GATE DENSITY.

- O FOR EACH PATH, HAS THE INPUT AND OUTPUT BEEN IDENTIFIED AND HAS THE EXPECTED WORST-CASE MAXIMUM PROPAGATION DELAY BEEN COMPUTED?

- O PROPAGATION DELAY MEASUREMENTS REQUIRED: BACK-ANNOTATION PATH DELAYS MUST BE SUPPLIED (BY IMPLEMENTATION ENGINEERING AT PRESENT)

- O TESTS ARE DONE AT MINIMUM AND MAXIMUM SUPPLY VOLTAGES

- o STANDARD RESISTOR/CAPACITOR LOAD ONLY (REFERENCE SPECIFICATION TS154)

#### SPECIAL AC TEST (PACKAGED PARTS ONLY)

- o ATE

- O UP TO 20MHz RATE (STANDARD RATE IS 10MHz)

- o t<sub>s</sub>/t<sub>h</sub> TEST VECTOR REQUIREMENTS ARE THE SAME AS FOR DELAY TESTS

#### BENCH TESTS

- O ARE BENCH TESTS REQUIRED? THESE TESTS ARE CHARACTERIZATION ONLY

- o CLOCK:  $f_{max}$  OF UP TO 350MHz WITH A MAXIMUM OF FOUR (4) DYNAMIC SIGNALS AND A MAXIMUM OF FIVE (5) CRITICAL PATHS.

- o MEASURE t<sub>r</sub>, t<sub>f</sub>

- o MEASURE  $t_{w}$  MINIMUM DOWN TO 2ns WITH THE SAME REQUIREMENT AS THE  $f_{max}$  TESTS.

- O BIASING CONDITIONS TO ESTABLISH CRITICAL PATHS MUST BE DEFINED

## TEGAS5 PROGRAM RESTRICTIONS [ MANUAL ]

- O NON-HIERARCHICAL MODULE NETLIST ONLY

- O ALL STATEMENTS MUST END WITH A \$

- o SIGNAL NAMES MUST BE <= 7 CHARACTERS

- O NO COLONS SHOULD APPEAR ANYWHERE IN THE PROGRAM

- O NO BLANK LINES SHOULD APPEAR ANYWHERE IN THE PROGRAM

- O COMMENTS ARE CREATED WITHIN DOUBLE QUOTES "THIS IS A COMMENT"

- O A DESCRIPTION SECTION MUST BE INCLUDED TO IDENTIFY THE DESIGNER AND THE DATE THAT THE PROGRAM WAS CREATED/MODIFIED, THE COMPANY NAME AND THE CIRCUIT NAME (AMCC REQUIREMENT)

O ANY STATEMENT IN THE DEFINE SECTION THAT IS NOT GND = GRND \$

MUST HAVE ALL SIGNALS EXPLICITLY CONNECTED TO PINS B01(PO\_560=Z,PO\_32=ZN) = GT36(LOADN=A,PO\_12=B,PO\_13=GND) \$

O THE EXCEPTION TO THE ABOVE, IF A PIN IS CONNECTED TO AN OUTPUT TERMINATOR, THEN THAT PIN AND ITS SIGNAL MUST BE OMITTED FROM THE STATEMENT

B01(PO\_560=Z,PO\_32=ZN) = GT36(LOADN=A,PO\_13=GND) \$

O IF OUTPUT SIGNALS ARE CONNECTED (WIRE-OR) THEN A WIREOR STATEMENT MUST REFLECT THIS CONDITION.

WO3(CALK=Z) = WIREOR4(SIG1=A,SIG2=B,SIG3=C,FRM=D) \$

Reference: AMCC packaging guide

#### PACKAGE SELECTION

- O REFER TO THE PACKAGING DOCUMENTATION FROM AMCC FOR THE LATEST SELECTION OF PACKAGES.

- O VARIOUS STANDARD PACKAGES ARE AVAILABLE. SPECIAL PACKAGING NEEDS CAN BE EVALUATED ON REQUEST.

- O CONTACT AMCC FOR PACKAGING DETAILS.

#### AMCC SUMMARY OF CONVENTIONS FOR SCHEMATICS

- Use 4-6 Alphanumeric characters (A-Z, 0-9) for all macro names and for all wire names

- All macros must be named

- Do not use macro pin names as macro or wire names

- All names must be unique within a circuit

- All inter- and intra- page connections and all off-chip connections must be named - name the wire and NOT the connector

- All inter- and intra- page connections must be commented as to the pages to which they go to/come from

- All I/O macros must be commented as to type and use

(ECL, TTL, TTLMIX, +5V ECL, simultaneously switching, etc.)

- All unused inputs are grounded (except AND inputs)

tie them to an inverter whose input is grounded

- Ground is a global name

- All unused outputs are terminated

- Terminators are not named

- All pages must be numbered, should be named for EWS

- WIREORx macros are named

- Follow AMCC naming conventions:

| A   | =   | Adder             |

|-----|-----|-------------------|

| B   | =   | Buffer            |

| G   | =   | Gate              |

| EX  | E   | Exclusive or/nor  |

| M   | =   | Mux               |

| DE  | =   | Decoder           |

| F   | *   | Flip flop         |

| L   | *** | Latch             |

| MM  | =   | Memory module     |

| MI  | =   | MSI macro         |

| SP  | =   | Special cell      |

| L S | =   | Inputs            |

| D   | 2   | Outputs           |

| BD  | *   | Bidirectional I/O |

| W   | *   | Wireors           |

| x   | 2   | None of the above |

# AMCC Bipolar Array Design Submission

DAISY

AMCC reserves the right to make changes to any products herein to improve the reliability, function or design. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

A M C C

APPLIED MICRO CIRCUITS CORPORATION

COPYRIGHT © 1985 ALL RIGHTS RESERVED DESIGN SUBMISSION DAISY LOGICIAN EWS

## SUBMITTING A BIPOLAR LOGIC ARRAY DESIGN TO AMCC

The following document has been designed to insure you, the customer, of a successful transition from concept to finished part. It is a summary of the items required for the submission of a bipolar array design to AMCC, when the schematic capture and test vector generation has been performed. These items should be submitted to AMCC for use in the acceptance design review prior to committing the design to layout.

This list was prepared for those customers who design with the  $\underline{\text{DAISY}}$  engineering workstation (EWS).

These are the critical information transfer areas which, if not completed, could delay the acceptance of your circuit.

DESIGN SUBMISSION DAISY LOGICIAN EWS

## AMCC BIPOLAR ARRAY DESIGN SUBMISSION CHECKLIST (REQUIRED)

The AMCC ERC software checks a large number of the possible design/schematic errors that can be made. There are a number of other checks that must be done by the customer prior to submission, including checks for test vector generation and submission. Attached to this document is the AMCC BIPOLAR ARRAY DESIGN SUBMISSION CHECKLIST. It must be filled in and submitted with the design documentation.

For reference, the individual design guides contain a design rules and guidelines summary for the particular array series. A more detailed listing of the design rules and guidelines, including the requirements for test vector generation, is included in the AMCC DESIGN VALIDATION REVIEW document.

Where an ERC report satisfies the required check requested in the validation review it is indicated by [ERC]. When an ERC report does not satisfy the required check, the check must be made by the designer and is indicated by [MANUAL]. AMCC will re-run the ERC software against the submitted design to ensure that all current design rules are being checked.

The design submission checklist is a summary of the documentation produced on completion of the design validation review.

DESIGN SUBMISSION DAISY LOGICIAN EWS

# MACRO LIBRARY VERSION AND DATE OF CREATION

A macro library version and date of drawing creation must be submitted as part of the hardcopy documentation. The version number of your library will be on the label on the release media (currently either floppy or tape).

## DRAWING PAGES (REQUIRED)

When a design is complete, the n.DRAW files are to be copied to floppydisks. The final version of the drawings are to be submitted. Make two sets minimum, one for submission and one for your own vaulting.

### ERC FILES (REQUIRED)

The AMCC ERC software is not system resident on the DAISY LOGICIAN (8086 or 80286) at this time. The software is currently run on the VAX. Hardcopies of the ERC run for the final design must be submitted.

## CRITICAL PATH SPECIFICATION (REQUIRED)

Maximum frequency of operation for the circuit required is related to the expected performance of the critical path(s) and should be clearly stated.

All paths that are critical in terms of timing margins (between calulated and specified delay) must be identified. The designer must supply the calculated worst-case timing for such critical path(s) and specify any additional performance or placement restrictions.

DESIGN SUBMISSION DAISY LOGICIAN EWS

## PREPLACEMENT/PREROUTE REQUESTS (OPTIONAL)

Preplacement/preroute requests can be submitted to AMCC for critical paths in a circuit if necessary. Preplacement and preroute requests will be evaluated by AMCC and the designer will be notified if they can or cannot be met.

## PIN-OUT REQUESTS (OPTIONAL)

I/O placement may be of concern in a design and the designer may wish to specify a pin-out request to AMCC. Pin-out is driven by layout requirements and AMCC will notify the customer if the desired pin-out can or cannot be achieved.

## SIMULTANEOUSLY SWITCHING OUTPUTS (REQUIRED)

Simultaneously switching outputs MUST be clearly identified and the designer must review the design to determine if the array requires additional TTL  $V_{\rm CC}$ , TTL GROUND or ECL GROUND pins.

DESIGN SUBMISSION DAISY LOGICIAN EWS

# SUBMITTING FUNCTIONAL TEST VECTORS (REQUIRED)

AMCC requires copies of EACH SOM control file (SOM\_MCF.SING) and its related DATA or INPUT file (if any). Hardcopies of these files must be submitted in addition to the copies submitted on floppy disks. These files must be commented as to company name, designer, circuit name (AMCC generated name for your design) and the date AT A MINIMUM. Additional comments as to tests performed or other information which documents the circuit are also required.

The SOM control file must reference the accompanying data file. The SOM control file MUST contain a PRINT\_ON\_CHANGE outputs section and the signals monitored MUST include:

- a. ALL INPUTS

- b. ALL OUTPUTS

- c. ALL INTERNAL THREE-STATE ENABLE CONTROL LINES

The data (or input) file must reference its SOM control file and

it must also describe the tests being performed.

The FORMAT file used in the simulation(s) must be included in the media submission. All test vectors must be generated using the same FORMAT file. DAISY software does not currently permit a hardcopy output of the FORMAT file with its accompanying sections on MODE, ACQUIRE, etc. When it is possible to do so, this file must also be submitted as part of the hardcopy documentation.

DESIGN SUBMISSION DAISY LOGICIAN EWS

#### SIMULATION RESULTS

The simulation output file must be included in the submitted media documentation. A hardcopy of the simulation output is also required.

AMCC requires a copy of the PRINT\_ON\_CHANGE output file for each simulation. The AMCCSIMFMT output file is also required.

The SIFT file name must be supplied (to identify the array, and the designer's selection of NOMINAL, COMMERCIAL or MILITARY timing parameters).

Any %SUBMIT procedures written by the customer to run the simulation must be included on the floppy disk containing that simulation. If none were used, a log of the VIEW, RUN and other step commands must be submitted (i.e., all commands used during the simulation file creation).

DESIGN SUBMISSION DAISY LOGICIAN EWS

## SUBMITTING "AT SPEED" TEST REQUIREMENTS TO AMCC (REQUIRED)

To verify that the array will operate at the required system dynamic frequency, a simulation of the array must be exercised at the required speed. This is currently a separate set of simulation vectors, with one line per clock change, scaled for actual time of change.

#### For example:

For the Q700, Q1500 on the DAISY LOGICIAN EWS, the simulation step is 0.1ns, so that a clock that changes at 10ns intervals has a vector at time = 0, 100, 200, 300, etc.

For the Q3500 series arrays on the same system, the scaling is different. The simulation step in this case is 0.01ns and the same clock, changing at 10ns intervals, would have a vector at time = 0, 1000, 2000, 3000, etc.

Scale the vectors according to the desired speed and the array involved.

The customer should be aware that the output states may not be well settled within the available vector period and that the apparent "phase delay" of some outputs relative to others makes the evaluation of "at speed" simulation results a non-trivial exercise.

AMCC is prepared to assist the customer in interpreting and understanding the results of such simulation.

DESIGN SUBMISSION DAISY LOGICIAN EWS

### AT SPEED SIMULATION DOCUMENTATION

The same basic documentation procedures must be followed for at-speed simulation submission as for functional simulation submission. The SOM control file must be commented, the data file (if any) must be commented, the FORMAT file must be supplied, the SIFT file name must be supplied (preferably by a comment in the SOM control file). The SIFT file identifies the design as COMMERCIAL or MILITARY.

The SOM control file must reference the accompanying data file. The SOM control file MUST contain a PRINT\_ON\_CHANGE outputs section and the signals monitored MUST include:

- a. ALL INPUTS

- b. ALL OUTPUTS

- c. ALL INTERNAL THREE-STATE ENABLE CONTROL LINES

The data (or input) file must reference its SOM control file and

it must also describe the tests being performed.

The at-speed simulation is run under DLS. There is no restriction on the VIEW and RUN commands as there is for the functional test vector simulation. A log of those commands as run must be submitted. The same FORMAT file must be used for all at speed simulations.

AMCC requires a copy of the PRINT\_ON\_CHANGE output file for each at speed simulation. The AMCCSIMFMT output file is also required.

DESIGN SUBMISSION DAISY LOGICIAN EWS

## AMCC AT SPEED PROCEDURE

AMCC will rerun the at speed simulation against the current DAISY library to verify operation.

# REQUESTING HARDWARE TESTING (OPTIONAL)

There is no routine hardware at-speed testing.

For speeds up to 50MHz, an HP test can be arranged. For speeds up to 125MHz, simple path (4 input limit) testing can be arranged (bench test).

Final at-speed verification is the customer's responsibility.

# REQUESTING PROPAGATION DELAY TESTING (OPTIONAL)

Propagation path measurement can be arranged. For each path, the input and output must be specified, and the worst-case maximum propagation delay computed (see the appropriate design guide). The list of paths and their documentation must be supplied if this test is desired.

Note: propagation delay testing requirements are subject to the limitations of the standard AMCC testers.

|                                                                                                                                                                                                                                   | PO #:<br>DATE:                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| AMCC DAISY DESIGN SUBMISSION CHECKLI                                                                                                                                                                                              | ST                            |

| COMPANY NAME:                                                                                                                                                                                                                     |                               |

| AMCC ASSIGNED CIRCUIT NAME (IF KNOWN):                                                                                                                                                                                            |                               |

| ARRAY:                                                                                                                                                                                                                            |                               |

| MACRO LIBRARY VERSION/DATE:                                                                                                                                                                                                       |                               |

| SIFT FILE NAME:                                                                                                                                                                                                                   | NOM COM MIL                   |

| FILES ON FLOPPY DISK(S):                                                                                                                                                                                                          |                               |

| [] DRAWING PAGES                                                                                                                                                                                                                  |                               |

| [] FUNCTIONAL TEST SUBMISSION: [] SOM CONTROL FILE(S) WITH DATA INPUT [] FORMAT FILE (ONLY ONE FOR ALL FUNCT) [] SIMULATION OUTPUT FILE(S) [] PRINT_ON_CHANGE OUTPUT FILE(S) [] %SUBMIT PROCEDURES OR [] LOG OF SIMULATION RUN(S) | FILE(S)<br>ONAL TEST VECTORS) |

| [] AC TEST SUBMISSION: [] SOM CONTROL FILE(S) WITH DATA INPUT [] FORMAT FILE (ONLY ONE FOR ALL AT-SPE [] SIMULATION OUTPUT FILE(S) [] PRINT_ON_CHANGE OUTPUT FILE(S) [] %SUBMIT PROCEDURES OR [] LOG OF SIMULATION RUN(S)         | FILE(S)<br>ED TEST VECTORS)   |

| HARDCOPY ENCLOSURES:                                                                                                                                                                                                              |                               |

## [] AC TEST SUBMISSION:

- [] SOM CONTROL FILE(S) WITH DATA IN

- [] FORMAT FILE (ONLY ONE FOR ALL AT

- [] SIMULATION OUTPUT FILE(S)

- [] PRINT\_ON\_CHANGE OUTPUT FILE(S)

- [] %SUBMIT PROCEDURES

#### HARDCOPY ENCLOSURES:

#### REQUIRED:

- [] ERC REPORTS

- [] CRITICAL PATH SPECIFICATION

- [] SIMULTANEOUSLY SWITCHING OUTPUTS

- [] SIMULATION OUTPUT FILE(S)

- [] DESIGN VALIDATION REVIEW HAS BEEN COMPLETED AND SUPPORTING DOCUMENTATION ENCLOSED

- [] updated NRE CHECKLIST

#### OPTIONAL:

- [] PIN-OUT REQUESTS

- [] PREPLACEMENT/PREROUTE REQUESTS

- [] HARDWARE TESTING DOCUMENTATION

- [] PROPAGATION DELAY TEST DOCUMENTATION